Managing The PC BIOS

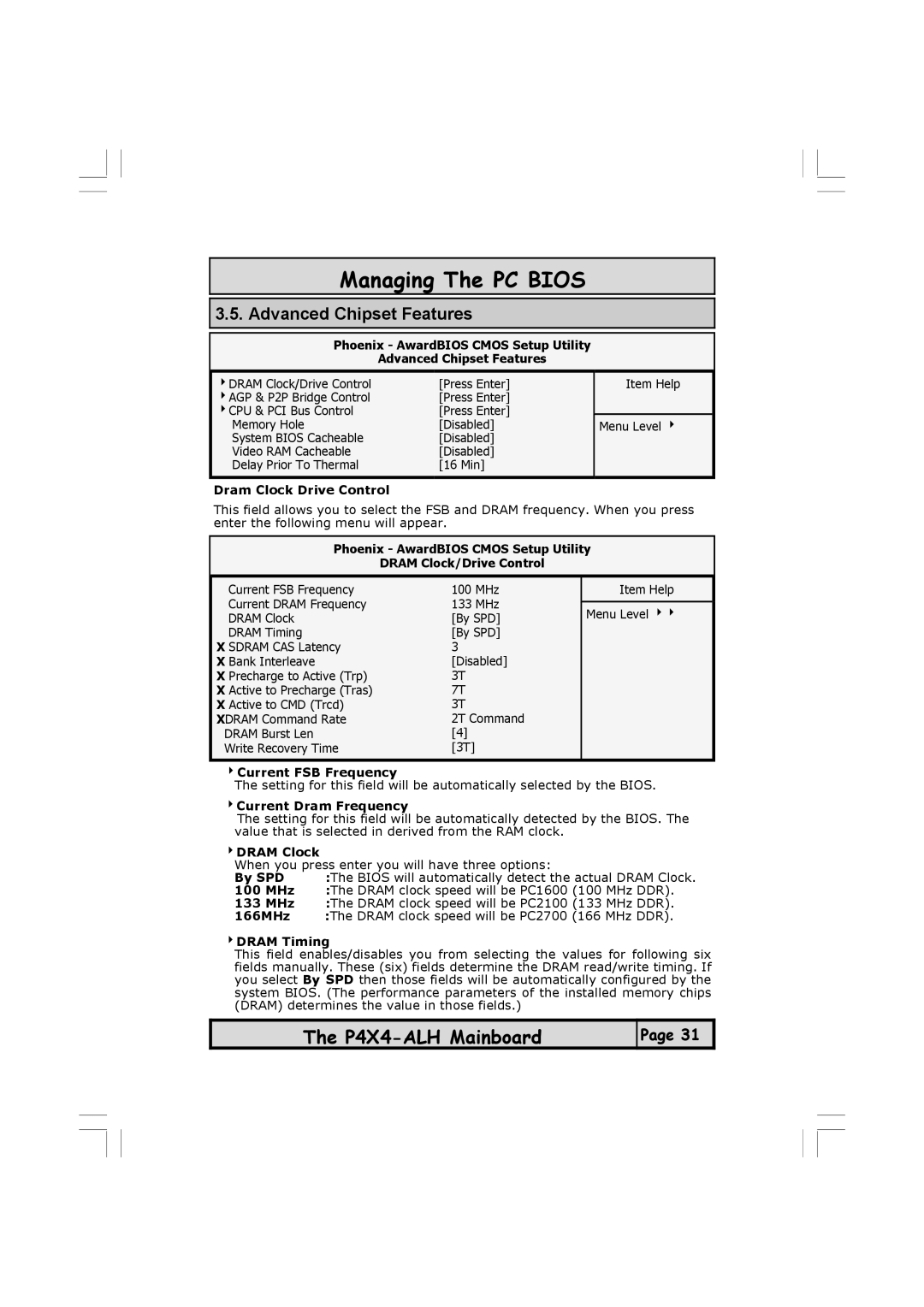

3.5. Advanced Chipset Features

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

4DRAM Clock/Drive Control | [Press Enter] |

4AGP & P2P Bridge Control | [Press Enter] |

4CPU & PCI Bus Control | [Press Enter] |

Memory Hole | [Disabled] |

System BIOS Cacheable | [Disabled] |

Video RAM Cacheable | [Disabled] |

Delay Prior To Thermal | [16 Min] |

Item Help

Menu Level 4

Dram Clock Drive Control

This field allows you to select the FSB and DRAM frequency. When you press enter the following menu will appear.

Phoenix - AwardBIOS CMOS Setup Utility

DRAM Clock/Drive Control

Current FSB Frequency | 100 MHz |

Current DRAM Frequency | 133 MHz |

DRAM Clock | [By SPD] |

DRAM Timing | [By SPD] |

X SDRAM CAS Latency | 3 |

X Bank Interleave | [Disabled] |

X Precharge to Active (Trp) | 3T |

X Active to Precharge (Tras) | 7T |

X Active to CMD (Trcd) | 3T |

XDRAM Command Rate | 2T Command |

DRAM Burst Len | [4] |

Write Recovery Time | [3T] |

Item Help

Menu Level 44

4Current FSB Frequency

The setting for this field will be automatically selected by the BIOS.

4Current Dram Frequency

The setting for this field will be automatically detected by the BIOS. The value that is selected in derived from the RAM clock.

4DRAM Clock

When you press enter you will have three options:

By SPD | :The BIOS will automatically detect the actual DRAM Clock. |

100 MHz | :The DRAM clock speed will be PC1600 (100 MHz DDR). |

133 MHz | :The DRAM clock speed will be PC2100 (133 MHz DDR). |

166MHz | :The DRAM clock speed will be PC2700 (166 MHz DDR). |

4DRAM Timing

This field enables/disables you from selecting the values for following six fields manually. These (six) fields determine the DRAM read/write timing. If you select By SPD then those fields will be automatically configured by the system BIOS. (The performance parameters of the installed memory chips (DRAM) determines the value in those fields.)

The

Page 31