Managing The PC BIOS

CPU & PCI Bus Control

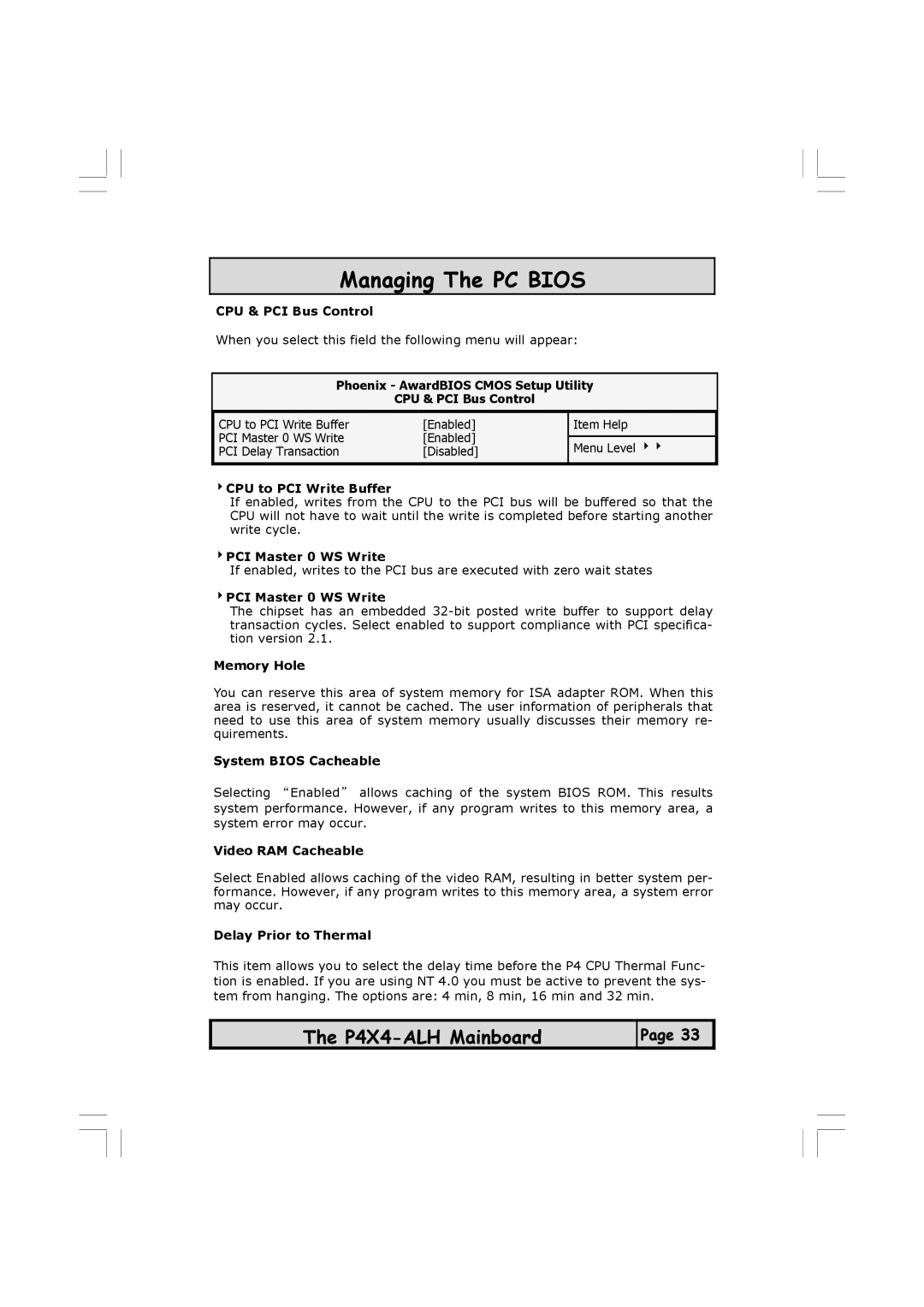

When you select this field the following menu will appear:

Phoenix - AwardBIOS CMOS Setup Utility

CPU & PCI Bus Control

CPU to PCI Write Buffer | [Enabled] |

PCI Master 0 WS Write | [Enabled] |

PCI Delay Transaction | [Disabled] |

Item Help

Menu Level 44

4CPU to PCI Write Buffer

If enabled, writes from the CPU to the PCI bus will be buffered so that the CPU will not have to wait until the write is completed before starting another write cycle.

4PCI Master 0 WS Write

If enabled, writes to the PCI bus are executed with zero wait states

4PCI Master 0 WS Write

The chipset has an embedded

Memory Hole

You can reserve this area of system memory for ISA adapter ROM. When this area is reserved, it cannot be cached. The user information of peripherals that need to use this area of system memory usually discusses their memory re- quirements.

System BIOS Cacheable

Selecting “Enabled” allows caching of the system BIOS ROM. This results system performance. However, if any program writes to this memory area, a system error may occur.

Video RAM Cacheable

Select Enabled allows caching of the video RAM, resulting in better system per- formance. However, if any program writes to this memory area, a system error may occur.

Delay Prior to Thermal

This item allows you to select the delay time before the P4 CPU Thermal Func- tion is enabled. If you are using NT 4.0 you must be active to prevent the sys- tem from hanging. The options are: 4 min, 8 min, 16 min and 32 min.

The

Page 33