UM10310_1 © NXP B.V. 2008. All rights reserved.

User manual Rev. 01 — 1 December 2008 108 of 139

NXP Semiconductors UM10310

P89LPC9321 User manual

The SRST bit in AUXR1 gives software the opportunity to reset the processor completely,

as if an external reset or watchdog reset had occurred. If a value is written to AUXR1 that

contains a 1 at bit position 3, all SFRs will be initialized and execution will resume at

program address 0000. Care should be taken when writing to AUXR1 to avoid accidental

software resets.

16.2 Dual Data PointersThe dual Data Pointers (DPTR) adds to the ways in which the processor can specify the

address used with certain instructions. The DPS bit in the AUXR1 register selects one of

the two Data Pointers. The DPTR that is not currently selected is not accessible to

software unless the DPS bit is toggled.

Specific instructions affected by the Data Pointer selection are:

INC DPTR — Increments the Data Pointer by 1

JMP@A+DPTR — Jump indirect relative to DPTR value

MOV DPTR, #data16 — Load the Data Pointer with a 16-bit constant

MOVC A, @A+DPTR — Move code byte relative to DPTR to the accumulator

MOVX A, @DPTR — Move accumulator to data memory relative to DPTR

MOVX @DPTR, A — Move from data memory relative to DPTR to the accumulator

Also, any instruction that reads or manipulates the DPH and DPL registers (the upper and

lower bytes of the current DPTR) will be affected by the setting of DPS. The MOVX

instructions have limited application for the P89LPC9321 since the part does not have an

external data bus. However, they may be used to access Flash configuration information

(see Flash Configuration section) or auxiliary data (XDATA) memory.

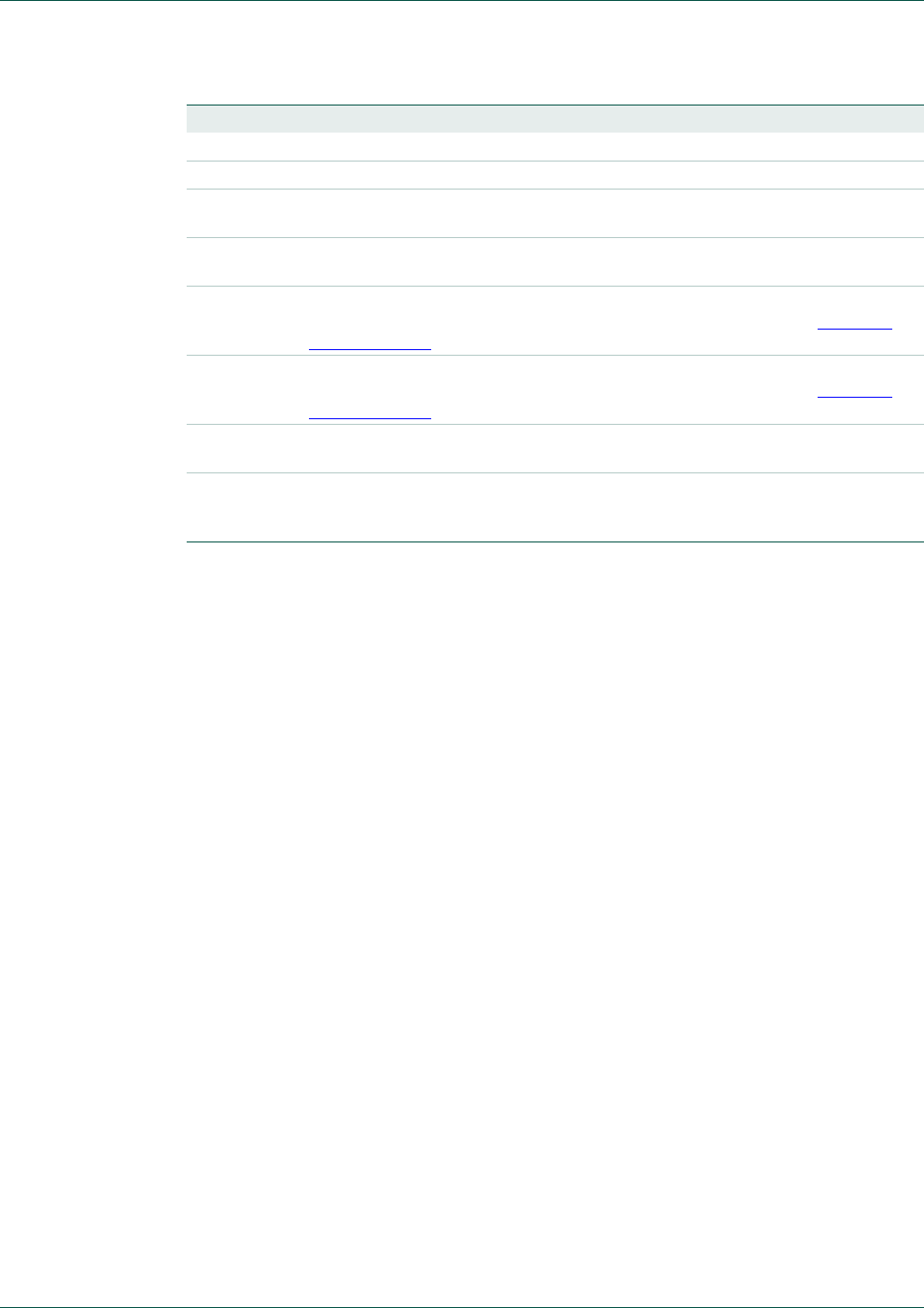

Table 102. AUXR1 register (address A2h) bit descri ption

Bit Symbol Description

0 DPS Data Pointer Select. Chooses one of two Data Pointers.

1 - Not used. Allowable to set to a logic 1.

2 0 This bit conta in s a ha rd-wired 0. Allows toggling of the DPS bit by incrementing

AUXR1, without interfering with other bits in the register.

3 SRST Software Reset. When set by software, resets the P89LPC9321 as if a hardware

reset occurred.

4 ENT0 When set the P1.2 pin is toggled whenever Timer 0 overflows. The output

frequency is therefore one half of the Timer 0 overflow rate. Refer to Section 7

“Timers 0 and 1” for details.

5 ENT1 When set, the P0.7 pin is toggled whenever Timer 1 overflows. The output

frequency is therefore one half of the Timer 1 overflow rate. Refer to Section 7

“Timers 0 and 1” for details.

6 EBRR UART Break Detect Reset Enable. If logic 1, UART Break Detect will cause a chip

reset and force the device into ISP mode.

7 CLKLP Clock Low Power Select. When set, reduces power consumption in the clock

circuits. Can be used when the clock frequency is 8MHz or less. After reset this bit

is cleared to support up to 12 MHz operation.