UM10310_1 © NXP B.V. 2008. All rights reserved.

User manual Rev. 01 — 1 December 2008 27 of 139

NXP Semiconductors UM10310

P89LPC9321 User manual

If the external interrupt is level-triggered, the external source must hold the request active

until the requested interrupt is generated. If the external interrupt is still asserted when the

interrupt service routine is completed, another interrupt will be generated. It is not

necessary to clear the interrupt flag IEn when the interrupt is level sensitive, it simply

tracks the input pin level.

If an external interrupt has been programmed as level-triggered and is enabled when the

P89LPC9321 is put into Power-down mode or Idle mode, the interrupt occurrence will

cause the processor to wake-up and resume operation. Refer to Section 5.3 “Power

reduction modes” for details. Note: the external interrupt must be programmed as

level-triggered to wake-up from Power-down mode.

3.2 External Interrupt pin glitch suppressionMost of the P89LPC9321 pins have glitch suppression circuits to reject short glitches

(please refer to the P89LPC9321 data sheet, Dynamic characteristics for glitch filter

specifications). However, pins SDA/INT0/P1.3 and SCL/T0/P1.2 do not have the glitch

suppression circuits. Therefore, INT1 has glitch suppression while INT0 does not.

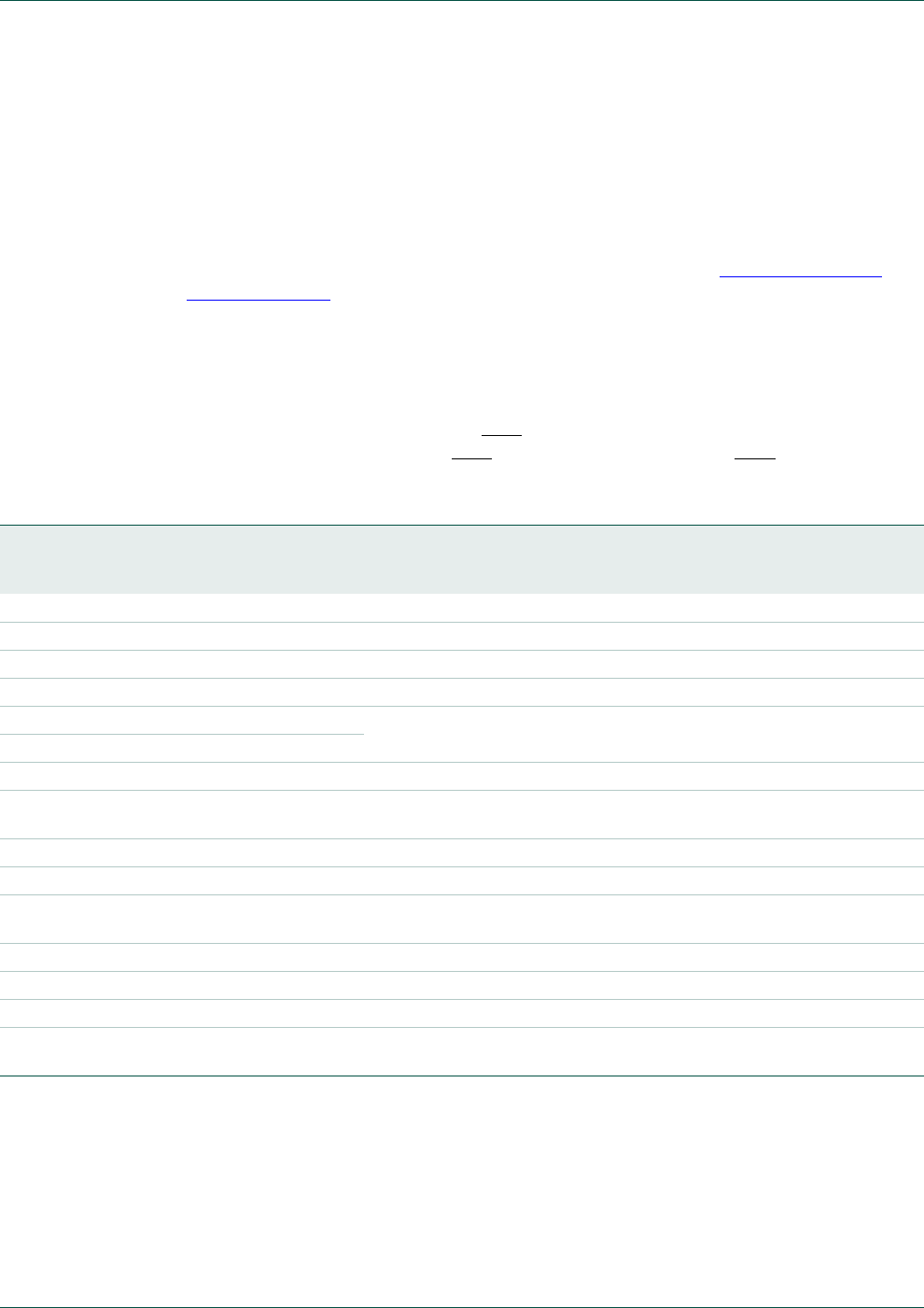

Table 11. Summary of interrupts

Description Interrupt flag

bit(s) Vector

address Interrupt enable

bit(s) Interrupt

priority Arbitration

ranking Power-

down

wake-up

External interrupt 0 IE0 0003h EX0 (IEN0.0) IP0H.0, IP0.0 1 (highest) Yes

Timer 0 interrupt T F0 000Bh ET0 (IEN0.1) IP0H.1, IP0.1 4 No

External interrupt 1 IE1 0013h EX1 (IEN0.2) IP0H.2, IP0.2 7 Yes

Timer 1 interrupt TF1 001Bh ET1 (IEN0.3) IP0H.3, IP0.3 10 No

Serial port Tx and Rx TI and RI 0023h ES/ESR (IEN0.4) IP0H.4, IP0.4 13 No

Serial port Rx RI

Brownout detect BOIF 002Bh EBO (IEN0.5) IP0H.5, IP0.5 2 Yes

Watchdog timer/Real-time

clock WDOVF/RTCF 0053h EWDRT (IEN0.6) IP0H.6, IP0.6 3 Yes

I2C interrupt SI 0033h EI2C (IEN1.0) IP0H.0, IP0.0 5 No

KBI interrupt KBIF 003Bh EKBI (IEN1.1) IP0H.0, IP0.0 8 Yes

Comparators 1 and 2

interrupts CMF1/CMF2 0043h EC (IEN1.2) IP0H.0, IP0.0 11 Yes

SPI interrupt SPIF 004Bh ESPI (IEN1.3) IP1H.3, IP1.3 14 No

Capture/Compare Unit 005Bh ECCU(IEN1.4) IP1H.4, IP1.4 6 No

Serial port Tx TI 006Bh EST (IEN1.6) IP0H.0, IP0.0 12 No

Data EEPROM write

complete 0073h EAD (IEN1.7) IP1H.7, IP1.7 15 (lowest) No