UM10310_1 © NXP B.V. 2008. All rights reserved.

User manual Rev. 01 — 1 December 2008 33 of 139

NXP Semiconductors UM10310

P89LPC9321 User manual

5. Power monitoring functionsThe P89LPC9321 incorporates power monitoring functions designed to prevent incorrect

operation during initial power-on and power loss or reduction during operation. This is

accomplished with two hardware functions: Power-on Detect and Brownout Detect.

5.1 Brownout detection

The brownout detect function determines if the power supply voltage drops below a

certain level. Enhanced BOD has 3 independent functions: BOD reset, BOD interrupt and

BOD EEPROM/FLASH.

BOD reset will cause a processor reset and it is always on, except in total power-down

mode. It could not be disabled in software. BOD interrupt will generate an interrupt and

could be enabled or disabled in software.

BOD reset and BOD interrupt, each has 4 trip voltage levels. BOE1 bit (UCFG1.5) and

BOE0 bit (UCFG1.3) are used as trip point configuration bits of BOD reset. BOICFG1 bit

and BOICFG0 bit in register BODCFG are used as trip point configuration bits of BOD

interrupt. BOD reset voltage should be lower than BOD interrupt trip point. Tabl e 15 gives

BOD trip points configuration.

In total power-down mode (PMOD1/PMOD0 = '11'), the circuitry for the Brownout

Detection is disabled for lowest power consumption. When PMOD1/PMOD0 not equal to

'11', BOD reset is always on and BOD interrupt is enabled by setting BOI (PCON.4) bit.

Please refer Table16 for BOD reset and BOD interrupt configuration. BOF bit

(RSTSRC.5), BOD reset flag is default as '0' and is set when BOD reset is tripped. BOIF

bit (RSTSRC.6), BOD interrupt flag is default as '0' and is set when BOD interrupt is

tripped.

BOD EEPROM/FLASH is used for flash/Data EEPROM program/erase protection. BOD

EEPROM/FLASH is always on, except in power-down or total power down mode

(PCON.1=1). It can not be disabled in software. BOD EEPROM/FLASH has only 1 trip

voltage level of 2.4 V. When voltage supply is lower than 2.4V, the BOD

EEPROM/FLASH is tripped and flash/Data EEPROM program/erase is blocked.

If brownout detection is enabled the brownout condition occurs when VDD falls below the

brownout trip voltage and is negated when VDD rises above the brownout trip voltage.

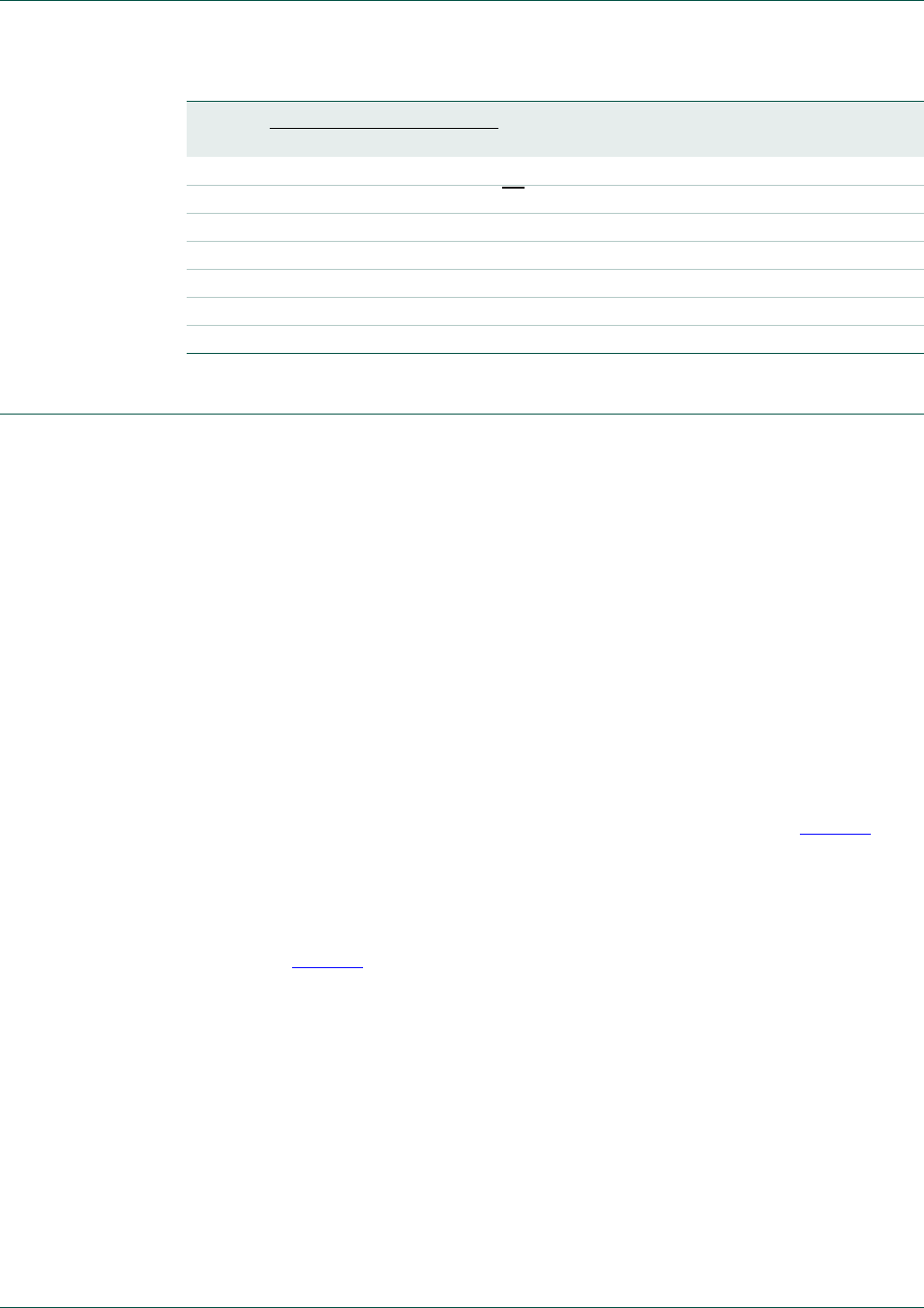

P2.3 P2M1.3 P2M2.3 MISO

P2.4 P2M1.4 P2M2.4 SS

P2.5 P2M1.5 P2M2.5 SPICLK

P2.6 P2M1.6 P2M2.6 OCA

P2.7 P2M1.7 P2M2.7 ICA

P3.0 P3M1.0 P3M2.0 CLKOUT, XTAL2

P3.1 P3M1.1 P3M2.1 XTAL1

Table 14. Port output configuration …continued

Port pin Configuration SFR bits

PxM1.y PxM2.y Alternate usage Notes