FrameSaver SLV

Copyright 2002 Paradyne Corporation All rights reserved

Contents

Contents

Index

Feature-Specific Configuration

Contents December

Purpose and Intended Audience

Document Organization

Section Description

Document Number Document Title

Product-Related Documents

FrameSaver SLV reference library contains

Other FrameSaver model-specific documentation includes

Vii

Conventions Used

Convention Used When Used

Configuration Procedures

Configuration Menu Example

Configuration Menu

Configuration Option Area Description

Configuration Option Areas

Main Menu→ Configuration

Accessing and Displaying Configuration Options

Configuration→PVC Connections

Changing Configuration Options

Saving Configuration Options

Basic Configuration

Main Menu→ Easy Install

Using the Easy Install Feature

Easy Install Screen Example DDS Interface

Service Type Possible Settings Frame Relay, Leased Line, PPP

Easy Install Configuration Options 1

Dslam

Easy Install Configuration Options 2

Create a Dedicated Network Management Link

Easy Install Configuration Options 3

Ethernet Management Options Screen

Time Slot Assignment Screen 9123, 9126

Network 1 Line Framing Format 9123, 9126

Easy Install Configuration Options 4

Network 1 Line Coding Format 9123, 9126

Network 1 Line Build Out 9520, 9520-ILM

Network 1 DSL Line Rate Mode 9720, 9783

Easy Install Configuration Options 5

DS0 Base Rate 9123, 9126

Network 1 Port Type 9820-2M, 9820-8M

Network 1 DSL Line Rate

Easy Install Configuration Options 6

384

784

Network 1 Channel

Easy Install Configuration Options 7

Configuration→Data Ports→DLCI Records

Using RIP with FrameSaver SLV CSU/DSUs

Entering System Information and Setting the System Clock

Main Menu→ Control→System Information

If the selection is Enter

Main Menu→ Auto-Configuration

Setting Up Auto-Configuration

Selecting a Frame Relay Discovery Mode

Main Menu→ Auto-Configuration→Frame Relay Discovery Mode

Discovery Mode Configuration Description

Takes place

Automatically Removing a Circuit

Configuration Option Tables

Configuration Options

Configuration Options

Configuring Frame Relay and LMI for the System CSU/DSUs

Configuring the Overall System

Main Menu→ Configuration→System →Frame Relay and LMI

System Frame Relay and LMI Options 1

System Frame Relay and LMI Options 2

System Frame Relay and LMI Options 3

LMI Status Enquiry N1 Possible Settings 1, 2, 3, 4

LMI Heartbeat T1 Possible Settings 5, 10, 15, 20, 25

System Frame Relay and LMI Options 4

Main Menu→ Configuration→System→PPP

Configuring PPP Options

Possible Settings Independent, Port-1FollowsNet

PPP Options

Field Setting After RfcCodePoints Selected

Configuring Class of Service Definitions

Class of Svc Name

Class of Service Definitions

Measure Latency & Availability

Code Points Assigned

Code Point Definitions

Code Point Definitions

Code Pnt

Name

Main Menu→ Configuration→System→Service Level Verification

Configuring Service Level Verification Options

Service Level Verification Options 1

SLV Type Available Settings Standard, COS 1-COS

Dlci Down on SLV Timeout

Service Level Verification Options 2

SLV Timeout Error Event Threshold

SLV Timeout Clearing Event Threshold

Service Level Verification Options 3

SLV Latency Clearing Event Threshold

SLV Packet Size bytes

Main Menu→ Configuration→System→General

Configuring General System Options

Test Timeout

General System Options 1

General System Options 2

General System Options 3

System Alarm Relay

Configuring Physical Interfaces

Configuring the Network Interface

Main Menu→ Configuration→Network→Physical

T1 Network Physical Interface Options 1

T1 Network Interface

Transmit Timing

T1 Network Physical Interface Options 2

Network Initiated LLB

Network Initiated PLB

T1 Network Physical Interface Options 3

Network Initiated Dclb Possible Settings Disable, V.54&ANSI

Ansi Performance Report Messages

ESF

Circuit Identifier

T1 Network Physical Interface Options 4

T3 Network Interface

T3 Network Physical Interface Options

Line Build Out

DDS Network Physical Interface Options 1

DDS Network Interface

DDS Network Physical Interface Options 2

DSU Latching Loopback

Require DSU Latching Loopback Preamble

Idsl Network Interface

Operating Rate Possible Settings AutoRate, 64, 128

10. Idsl Network Physical Interface Options

Channel

Sdsl Network Interface

Line Rate Mode Possible Settings Hunt, AutoRate, Fixed

11. Sdsl Network Physical Interface Options

DSL Line Rate Kbps

12. Shdsl Network Physical Interface Options 1

Shdsl Network Interface

12. Shdsl Network Physical Interface Options 2

Synchronous Network Interface

PSD Mask

Port Type

Monitor DSR

Monitor CTS

Monitor Rlsd

14. Hssi Network Data Port Physical Interface Options

Hssi Network Interface

Main Menu→ Configuration→Data Ports→Physical

Configuring a User Data Port CSU/DSUs

Data Port Physical Interface

15. V.35 Data Port Physical Interface Options 1

15. V.35 Data Port Physical Interface Options 2

Port Use Possible Settings Frame Relay, Synchronous Data

Max Port Rate

Port Base Rate

15. V.35 Data Port Physical Interface Options 3

Transmit Clock Source

Monitor RTS

15. V.35 Data Port Physical Interface Options 4

Monitor DTR

Port DTE Initiated Loopbacks

Action on Network Yellow Alarm

15. V.35 Data Port Physical Interface Options 5

Invert Transmit and Receive Data

15. V.35 Data Port Physical Interface Options 6

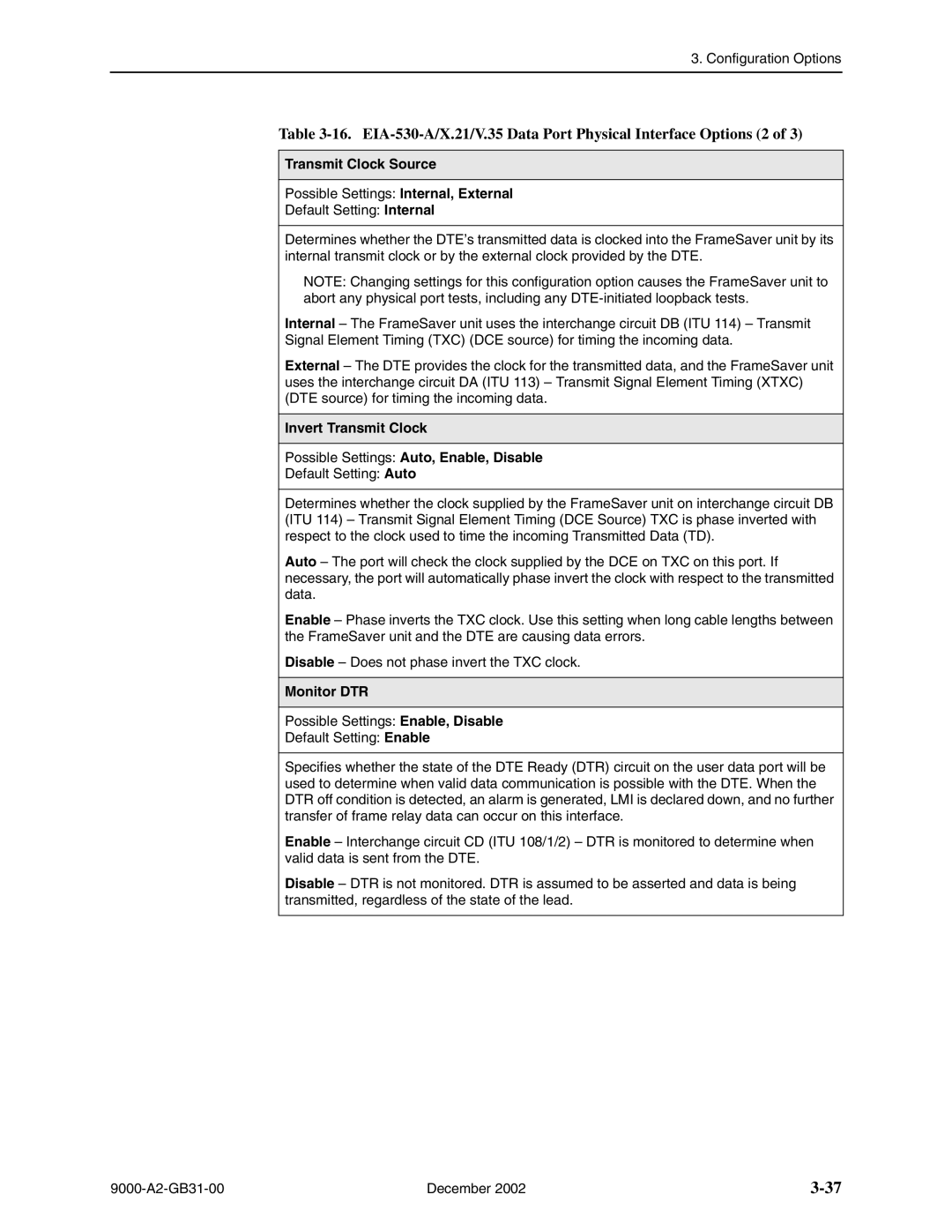

EIA-530-A/X.21/V.35 Data Port Physical Interface

Transmit Clock Source

17. Hssi Data Port Physical Interface Options 1

Hssi Data Port Physical Interface

17. Hssi Data Port Physical Interface Options 2

17. Hssi Data Port Physical Interface Options 3

Configuring the T3 User Port 9520-ILM

Main Menu→ Configuration→T3 User Ports→ Physical

18. T3 User Port Physical Interface Options

Main Menu→ Configuration→DSX-1

Configuring the DSX-1 Interface 9126

19. DSX-1 Physical Interface Options 1

Interface Status

Send All Ones on DSX-1 Failure

19. DSX-1 Physical Interface Options 2

Main Menu→ Configuration→ISDN→Physical

Configuring the Isdn DBM Interface 9126, 9128

Service Profile ID Spid 1 or

20. Isdn BRI DBM Physical Interface Options 9126

Switch Type Possible Settings NI-2, ATT4ESS, ATT5ESS

21. Isdn PRI DBM Physical Interface Options 9128 1

Local Phone Number

21. Isdn PRI DBM Physical Interface Options 9128 2

Line Build Out LBO Possible Settings 0.0, -7.5, -15

21. Isdn PRI DBM Physical Interface Options 9128 3

Main Menu→ Configuration→ISDN→ISDN Link Profiles

Setting Up Isdn Link Profiles 9126, 9128

22. Isdn Link Profile Options 1

Link Name

Outbound Phone Number

22. Isdn Link Profile Options 2

Inbound Calling ID 1 or

Maximum Link Rate Kbps

22. Isdn Link Profile Options 3

Assigning Time Slots/Cross Connections

Caller Identification Method

Alternate Outbound Phone Number

Assigning Time Slots to the Network Interface

Value Meaning

PPP

Assigning DSX-1 Time Slots to the Network Interface

DSX-1 to Network Time Slot Assignment Screen Example

DSX-1 Signaling Assignments and Trunk Conditioning

RBS

Idle

PLAR3idle

Synchronous Data Port Assignment Screen Example

Clearing Assignments

Configuring Frame Relay for an Interface

24. Interface Frame Relay Options 1

LMI

Traffic Policing

24. Interface Frame Relay Options 2

LMI Parameters

Frame Relay DS0s Base Rate

24. Interface Frame Relay Options 3

Configuring PPP for an Interface

Main Menu→ Configuration→Network/Data Ports → PPP

25. Interface PPP Options

Manually Configuring Dlci Records

26. Dlci Record Options 1

Dlci Number

CIR bps

26. Dlci Record Options 2

26. Dlci Record Options 3

Committed Burst Size Bc Bits

Excess Burst Size Bits

26. Dlci Record Options 4

Backup Group Possible Settings A, B, C, . . . Z, None

Dlci Priority

Outbound Management Priority

Main Menu →Configuration →Network →Circuit Records

Configuring Circuit Records for the Network Interface

27. Circuit Records Options 1

VPI,VCI Number

9783 0 9788 0

27. Circuit Records Options 2

27. Circuit Records Options 3

Excess Burst Size Be Bits

9783 9788

Main Menu→ Configuration→Network →ATM

Configuring ATM for the Network Interface

Cell Delineation Error Event Threshold

28. Network ATM Options

Main Menu→ Configuration→PVC Connections

Configuring PVC Connections

29. PVC Connection Options 1

Source Dlci

Source Edlci

29. PVC Connection Options 2

Primary Destination Link

Primary Destination Dlci

Primary Destination Edlci

29. PVC Connection Options 3

Alternate Destination Link

Alternate Destination Dlci

Alternate Destination Edlci

29. PVC Connection Options 4

Configuring the IP Path List

Main Menu→ Configuration→IP Path List Static

30. IP Path List

Setting Up Management and Communication Options

31. Node IP Options 1

Configuring Node IP Information

31. Node IP Options 2

TS Access Management Link

31. Node IP Options 3

Management MTU Size

TS Management Snmp Validation

31. Node IP Options 4

32. Management PVC Options 1

Configuring Management PVCs

32. Management PVC Options 2

Payload Managed

Set DE

Primary Dlci

32. Management PVC Options 3

Primary Edlci

32. Management PVC Options 4

32. Management PVC Options 5

Alternate Dlci

Alternate Edlci

Encapsulation

32. Management PVC Options 6

Name 1 Access

Configuring General Snmp Management

33. General Snmp Management Options 1

Snmp Management

Configuring Telnet and/or FTP Session Support

Name 2 Access

33. General Snmp Management Options 2

Telnet Login Required

34. Telnet and FTP Session Options 1

Telnet Session

34. Telnet and FTP Session Options 2

35. Snmp NMS Security Options 1

Configuring Snmp NMS Security

NMS IP Validation

Number of Managers

Configuring Snmp Traps and Trap Dial-Out

35. Snmp NMS Security Options 2

36. Snmp Traps and Trap Dial-Out Options 1

Link see -38, Communication Port Options

36. Snmp Traps and Trap Dial-Out Options 2

Link Traps Possible Settings Disable, Up, Down, Both

36. Snmp Traps and Trap Dial-Out Options 3

Enterprise Specific Traps

36. Snmp Traps and Trap Dial-Out Options 4

Possible Settings Network, Ports, DBM, All, None

Dlci Traps on Interfaces Filter Selection Field

Rmon Traps

36. Snmp Traps and Trap Dial-Out Options 5

Dial-Out Delay TIme Min

Trap Dial-Out

Trap Disconnect

Alternate Dial-Out Directory

36. Snmp Traps and Trap Dial-Out Options 6

Latency Traps

IP SLV Availability Traps

37. Ethernet Management Options 1

Configuring Ethernet Management

Proxy ARP

37. Ethernet Management Options 2

Configuring the Communication Port

38. Communication Port Options 1

Character Length

38. Communication Port Options 2

Login Required

Parity

Stop Bits

38. Communication Port Options 3

103

RIP

38. Communication Port Options 4

Configuring the Modem Port

38. Communication Port Options 5

39. Modem Port Options 1

39. Modem Port Options 2

106

39. Modem Port Options 3

107

39. Modem Port Options 4

Configuring the Criteria for Automatic Backup

Main Menu→ Configuration→Auto Backup Criteria

40. Auto Backup Criteria Options 1

When Auto Backup Allowed

40. Auto Backup Criteria Options 2

Backup Allowed Day From nnnn

Backup Allowed Day To nnnn

Feature-Specific Configuration

AT Command String To configure the modem to

Setting Up an External Modem

Setting Up Call Directories for Trap Dial-Out

Setting Up an Internal Modem

Main Menu→Control→Modem Call Directories

Valid characters include For

Setting Up to Use the Modem PassThru Feature

Setting Up Dial Backup

Setting Up the DBM Physical Interface

Main Menu→Configuration→ISDN→Physical

If you select Then

Setting Up Automatic Backup Configuration

Connections? PVC Connections?

Following prompt When Appears If you select

Criteria for Automatic Backup in , Configuration Options

Main Menu→Configuration→ISDN→Link Profiles

For Originating a Backup Call For Answering a Backup Call

Modifying Isdn Link Profiles

Main Menu→Configuration→Auto-Backup Criteria

Restricting Automatic Backup and Configuring Backup Timers

Assigning DLCIs to a Backup Group

Configuring the DBM Interface to Send Snmp Traps

Setting Up Back-to-Back Operation

PVC Backup Over the Network Interface

Changing Operating Mode

Main Menu→Control→Change Operating Mode

Feature-Specific Configuration 9000-A2-GB31-00 December

Feature-Specific Configuration December

ATM

ARP

DTR

DBM

Rlsd

RTS

EIR

DTE

DSL

Idsl

IP SLV

Isdn

Hssi

IN-5

NMS

IN-6

IP Slip

Snmp NMS

PVC

SLV

IN-8

IN-9

IN-10