SETTINGS OF CAMERA CONTROL AND STATUS REGISTER

SETTINGS OF CAMERA CONTROL AND STATUS REGISTER

![]() This chapter describes CSR addresses using the lower 32 bits of 64 bits. (CSR: Abbreviation of Control and Status Register) The omitted upper 32 bits are ∗∗∗∗FFFFh. (∗∗∗∗ changes according to the connection of the IEEE1394 Serial Bus.)

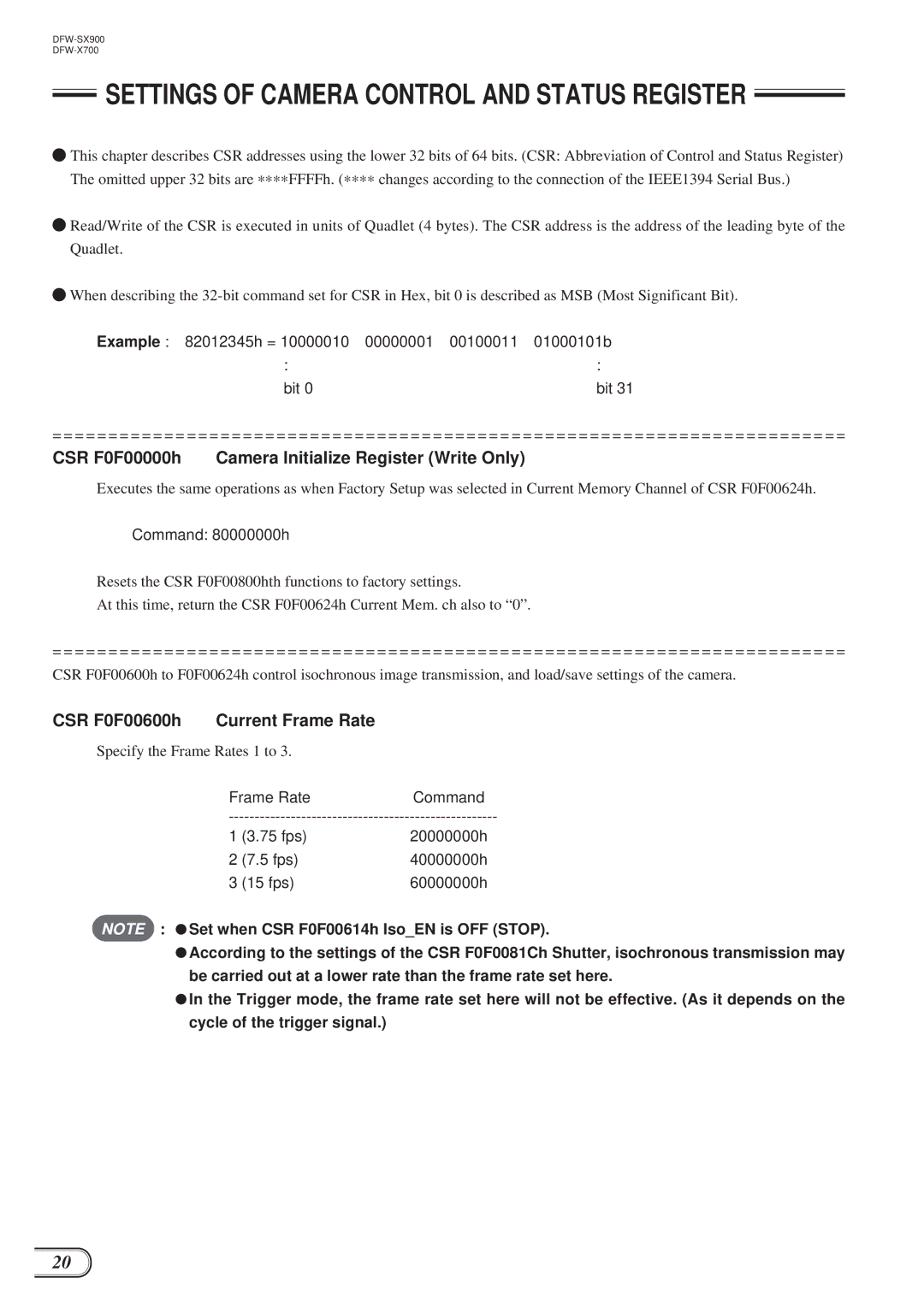

This chapter describes CSR addresses using the lower 32 bits of 64 bits. (CSR: Abbreviation of Control and Status Register) The omitted upper 32 bits are ∗∗∗∗FFFFh. (∗∗∗∗ changes according to the connection of the IEEE1394 Serial Bus.)

![]() Read/Write of the CSR is executed in units of Quadlet (4 bytes). The CSR address is the address of the leading byte of the Quadlet.

Read/Write of the CSR is executed in units of Quadlet (4 bytes). The CSR address is the address of the leading byte of the Quadlet.

![]() When describing the

When describing the

Example : 82012345h = 10000010 | 00000001 00100011 01000101b |

: | : |

bit 0 | bit 31 |

= = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = =

CSR F0F00000h Camera Initialize Register (Write Only)

Executes the same operations as when Factory Setup was selected in Current Memory Channel of CSR F0F00624h.

Command: 80000000h

Resets the CSR F0F00800hth functions to factory settings.

At this time, return the CSR F0F00624h Current Mem. ch also to “0”.

= = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = = =

CSR F0F00600h to F0F00624h control isochronous image transmission, and load/save settings of the camera.

CSR F0F00600h | Current Frame Rate |

| |

Specify the Frame Rates 1 to 3. |

| ||

| Frame Rate | Command | |

| |||

| 1 | (3.75 fps) | 20000000h |

| 2 | (7.5 fps) | 40000000h |

| 3 | (15 fps) | 60000000h |

NOTE : ![]() Set when CSR F0F00614h Iso_EN is OFF (STOP).

Set when CSR F0F00614h Iso_EN is OFF (STOP).

![]() According to the settings of the CSR F0F0081Ch Shutter, isochronous transmission may be carried out at a lower rate than the frame rate set here.

According to the settings of the CSR F0F0081Ch Shutter, isochronous transmission may be carried out at a lower rate than the frame rate set here.

![]() In the Trigger mode, the frame rate set here will not be effective. (As it depends on the cycle of the trigger signal.)

In the Trigger mode, the frame rate set here will not be effective. (As it depends on the cycle of the trigger signal.)

20