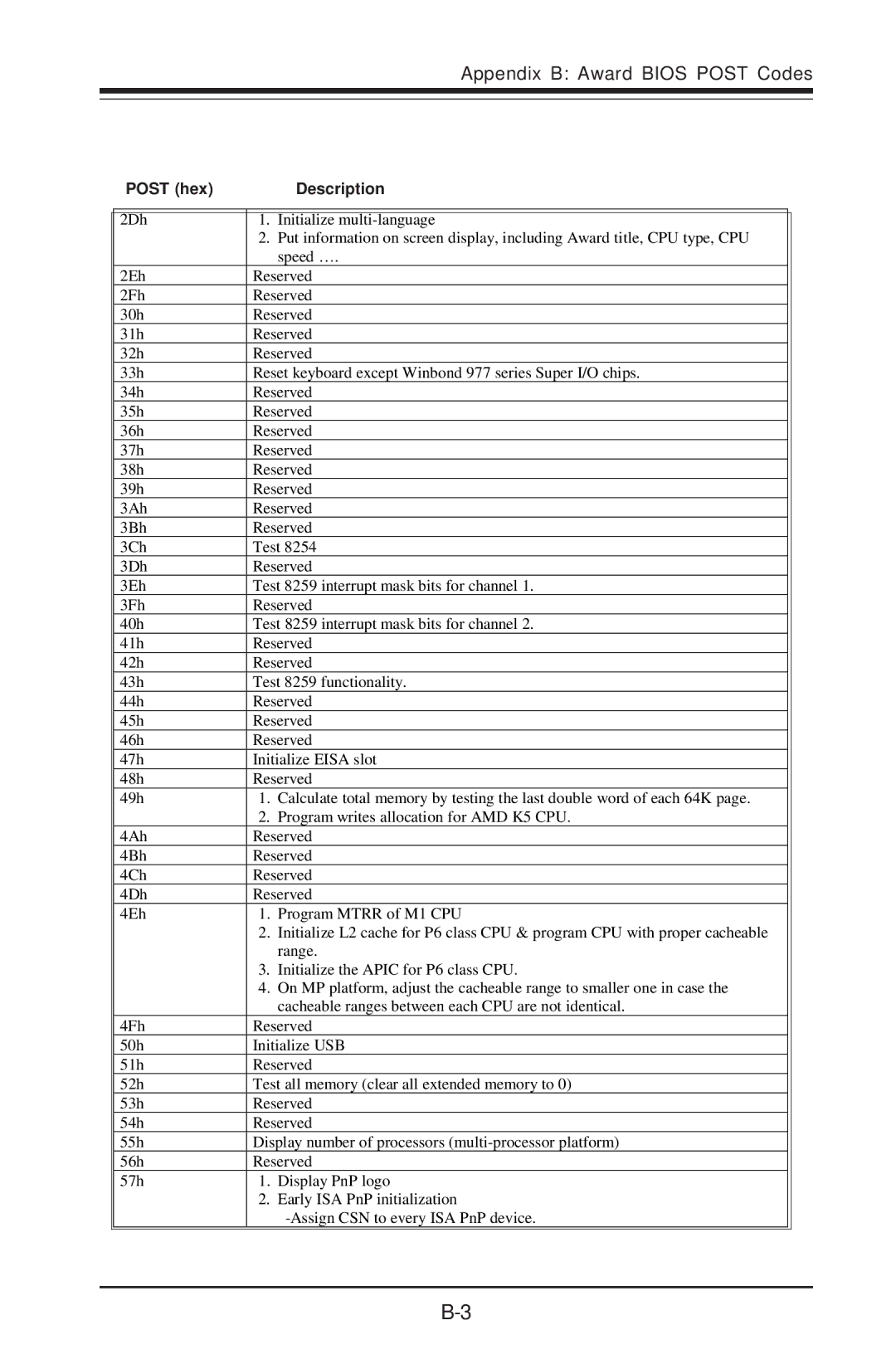

Appendix B: Award BIOS POST Codes

POST (hex) | Description |

|

|

2Dh | 1. Initialize |

| 2. Put information on screen display, including Award title, CPU type, CPU |

| speed …. |

2Eh | Reserved |

2Fh | Reserved |

30h | Reserved |

31h | Reserved |

32h | Reserved |

33h | Reset keyboard except Winbond 977 series Super I/O chips. |

34h | Reserved |

35h | Reserved |

36h | Reserved |

37h | Reserved |

38h | Reserved |

39h | Reserved |

3Ah | Reserved |

3Bh | Reserved |

3Ch | Test 8254 |

3Dh | Reserved |

3Eh | Test 8259 interrupt mask bits for channel 1. |

3Fh | Reserved |

40h | Test 8259 interrupt mask bits for channel 2. |

41h | Reserved |

42h | Reserved |

43h | Test 8259 functionality. |

44h | Reserved |

45h | Reserved |

46h | Reserved |

47h | Initialize EISA slot |

48h | Reserved |

49h | 1. Calculate total memory by testing the last double word of each 64K page. |

| 2. Program writes allocation for AMD K5 CPU. |

4Ah | Reserved |

4Bh | Reserved |

4Ch | Reserved |

4Dh | Reserved |

4Eh | 1. Program MTRR of M1 CPU |

| 2. Initialize L2 cache for P6 class CPU & program CPU with proper cacheable |

| range. |

| 3. Initialize the APIC for P6 class CPU. |

| 4. On MP platform, adjust the cacheable range to smaller one in case the |

| cacheable ranges between each CPU are not identical. |

4Fh | Reserved |

50h | Initialize USB |

51h | Reserved |

52h | Test all memory (clear all extended memory to 0) |

53h | Reserved |

54h | Reserved |

55h | Display number of processors |

56h | Reserved |

57h | 1. Display PnP logo |

| 2. Early ISA PnP initialization |

| |

|

|