www.ti.com

VLYNQ Port Registers

3.6Interrupt Pending/Set Register (INTPENDSET)

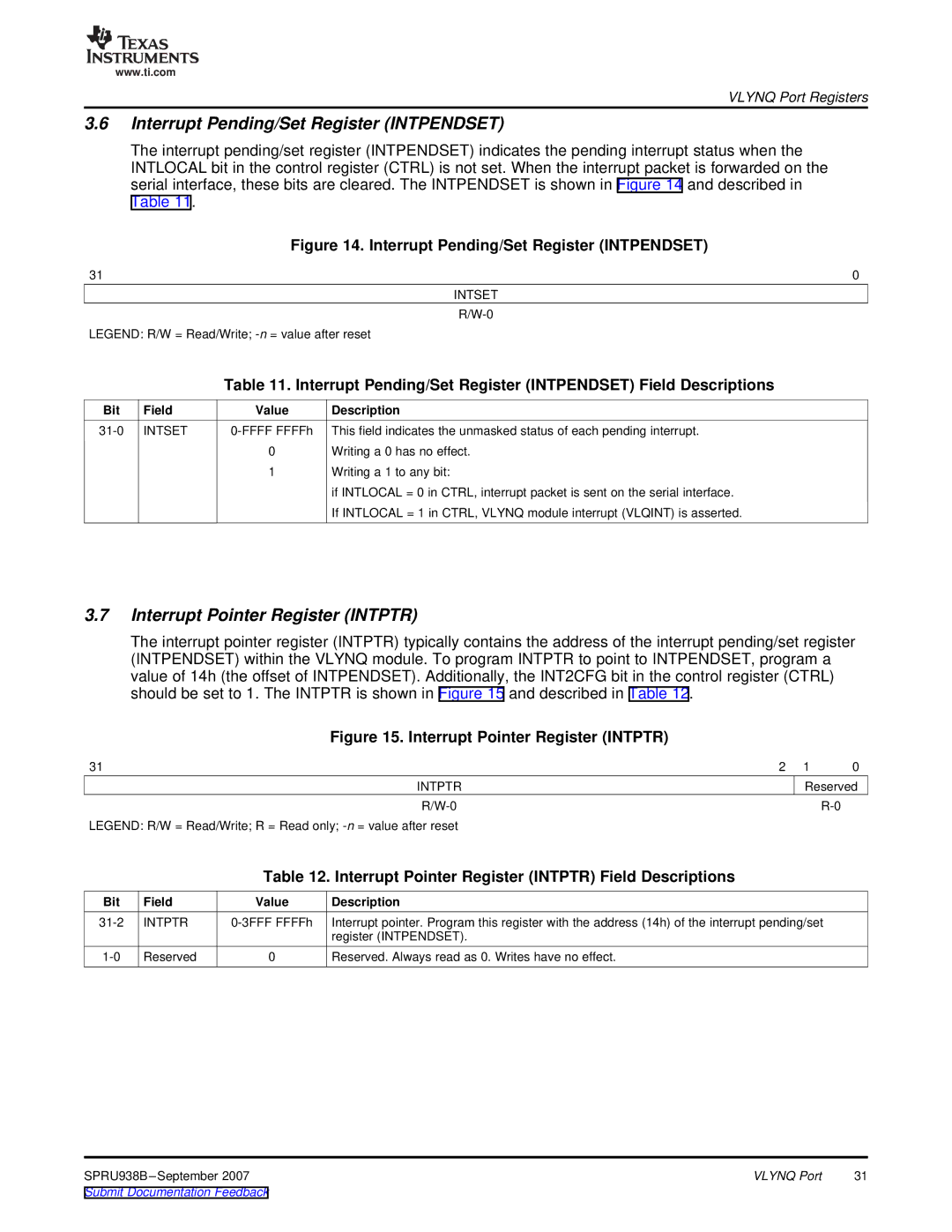

The interrupt pending/set register (INTPENDSET) indicates the pending interrupt status when the INTLOCAL bit in the control register (CTRL) is not set. When the interrupt packet is forwarded on the serial interface, these bits are cleared. The INTPENDSET is shown in Figure 14 and described in Table 11.

Figure 14. Interrupt Pending/Set Register (INTPENDSET)

31 | 0 |

INTSET

LEGEND: R/W = Read/Write;

Table 11. Interrupt Pending/Set Register (INTPENDSET) Field Descriptions

Bit | Field | Value | Description |

INTSET | This field indicates the unmasked status of each pending interrupt. | ||

|

| 0 | Writing a 0 has no effect. |

|

| 1 | Writing a 1 to any bit: |

|

|

| if INTLOCAL = 0 in CTRL, interrupt packet is sent on the serial interface. |

|

|

| If INTLOCAL = 1 in CTRL, VLYNQ module interrupt (VLQINT) is asserted. |

3.7Interrupt Pointer Register (INTPTR)

The interrupt pointer register (INTPTR) typically contains the address of the interrupt pending/set register (INTPENDSET) within the VLYNQ module. To program INTPTR to point to INTPENDSET, program a value of 14h (the offset of INTPENDSET). Additionally, the INT2CFG bit in the control register (CTRL) should be set to 1. The INTPTR is shown in Figure 15 and described in Table 12.

Figure 15. Interrupt Pointer Register (INTPTR)

31 | 2 | 1 | 0 |

INTPTR |

| Reserved | |

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

Table 12. Interrupt Pointer Register (INTPTR) Field Descriptions

Bit | Field | Value | Description |

INTPTR |

| Interrupt pointer. Program this register with the address (14h) of the interrupt pending/set | |

|

|

| register (INTPENDSET). |

Reserved | 0 | Reserved. Always read as 0. Writes have no effect. |

SPRU938B | VLYNQ Port | 31 |

Submit Documentation Feedback |

|

|