www.ti.com

VLYNQ Port Registers

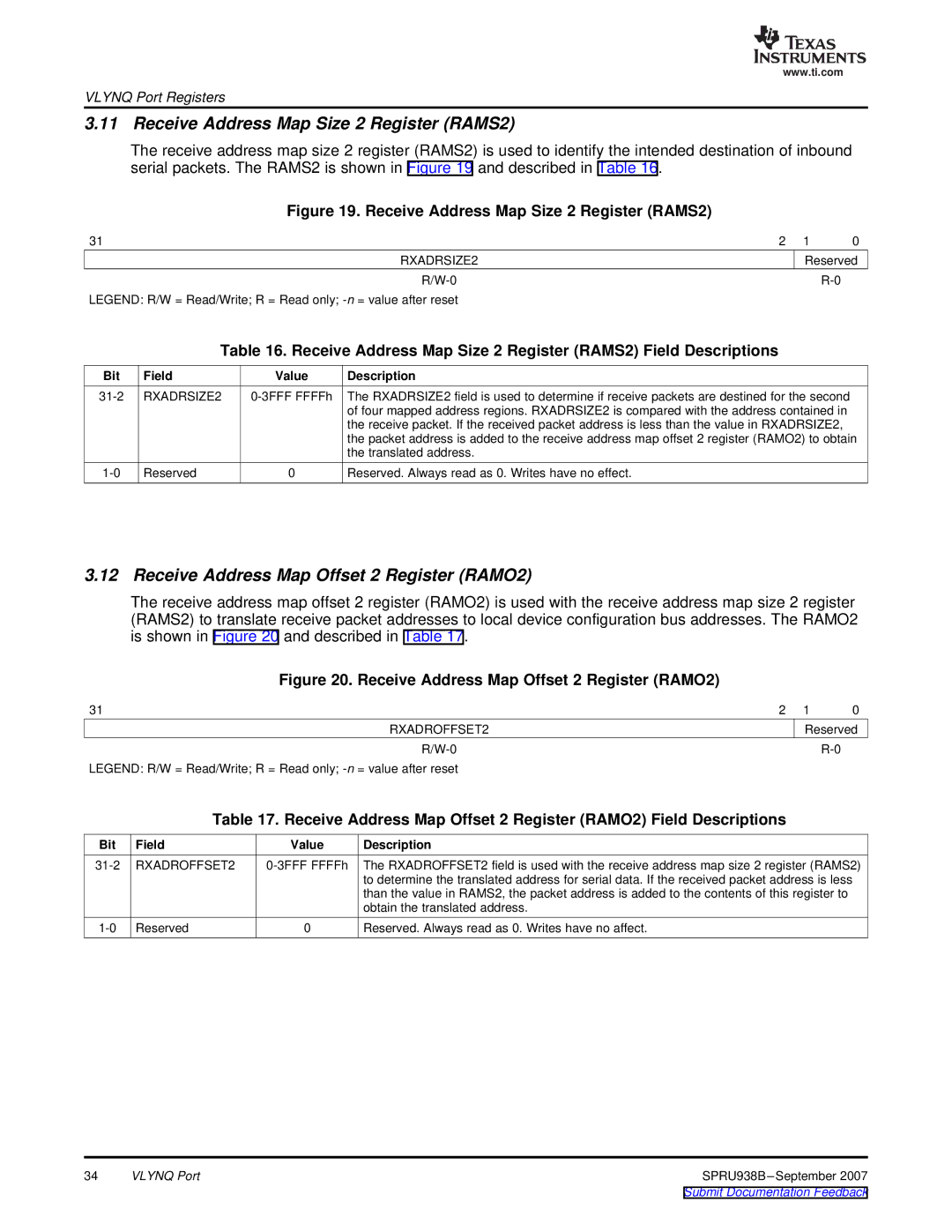

3.11 Receive Address Map Size 2 Register (RAMS2)

The receive address map size 2 register (RAMS2) is used to identify the intended destination of inbound serial packets. The RAMS2 is shown in Figure 19 and described in Table 16.

Figure 19. Receive Address Map Size 2 Register (RAMS2)

31 | 2 | 1 | 0 |

RXADRSIZE2 |

| Reserved | |

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

Table 16. Receive Address Map Size 2 Register (RAMS2) Field Descriptions

Bit | Field | Value | Description |

RXADRSIZE2 | The RXADRSIZE2 field is used to determine if receive packets are destined for the second | ||

|

|

| of four mapped address regions. RXADRSIZE2 is compared with the address contained in |

|

|

| the receive packet. If the received packet address is less than the value in RXADRSIZE2, |

|

|

| the packet address is added to the receive address map offset 2 register (RAMO2) to obtain |

|

|

| the translated address. |

Reserved | 0 | Reserved. Always read as 0. Writes have no effect. |

3.12 Receive Address Map Offset 2 Register (RAMO2)

The receive address map offset 2 register (RAMO2) is used with the receive address map size 2 register (RAMS2) to translate receive packet addresses to local device configuration bus addresses. The RAMO2 is shown in Figure 20 and described in Table 17.

Figure 20. Receive Address Map Offset 2 Register (RAMO2)

31 | 2 | 1 | 0 |

RXADROFFSET2 |

| Reserved | |

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

Table 17. Receive Address Map Offset 2 Register (RAMO2) Field Descriptions

Bit | Field | Value | Description |

RXADROFFSET2 |

| The RXADROFFSET2 field is used with the receive address map size 2 register (RAMS2) | |

|

|

| to determine the translated address for serial data. If the received packet address is less |

|

|

| than the value in RAMS2, the packet address is added to the contents of this register to |

|

|

| obtain the translated address. |

Reserved | 0 | Reserved. Always read as 0. Writes have no affect. |

34 | VLYNQ Port | SPRU938B |