www.ti.com

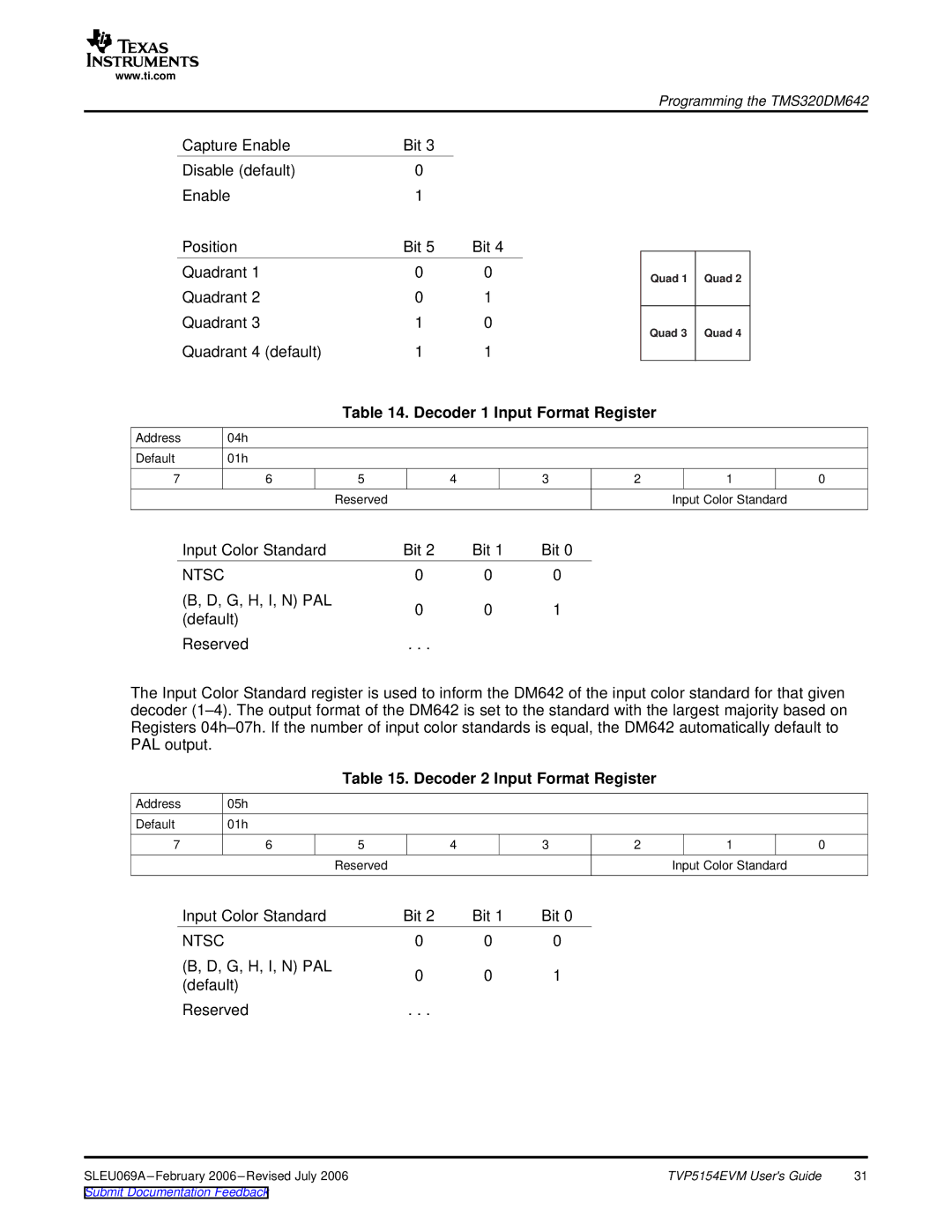

Capture Enable | Bit 3 |

|

Disable (default) | 0 |

|

Enable | 1 |

|

Position | Bit 5 | Bit 4 |

Quadrant 1 | 0 | 0 |

Quadrant 2 | 0 | 1 |

Quadrant 3 | 1 | 0 |

Quadrant 4 (default) | 1 | 1 |

Programming the TMS320DM642

Quad 1 | Quad 2 |

|

|

Quad 3 | Quad 4 |

|

|

Table 14. Decoder 1 Input Format Register

Address | 04h |

|

|

|

|

|

|

Default | 01h |

|

|

|

|

|

|

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| Reserved |

|

|

| Input Color | Standard |

Input Color Standard

NTSC

(B, D, G, H, I, N) PAL (default)

Reserved

Bit 2 | Bit 1 | Bit 0 |

0 0 0

0 0 1

. . .

The Input Color Standard register is used to inform the DM642 of the input color standard for that given decoder

Table 15. Decoder 2 Input Format Register

Address | 05h |

|

|

|

|

|

|

Default | 01h |

|

|

|

|

|

|

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| Reserved |

|

|

| Input Color | Standard |

Input Color Standard

NTSC

(B, D, G, H, I, N) PAL (default)

Reserved

Bit 2 | Bit 1 | Bit 0 |

0 | 0 | 0 |

0 | 0 | 1 |

. . . |

|

|

SLEU069A | TVP5154EVM User's Guide | 31 |