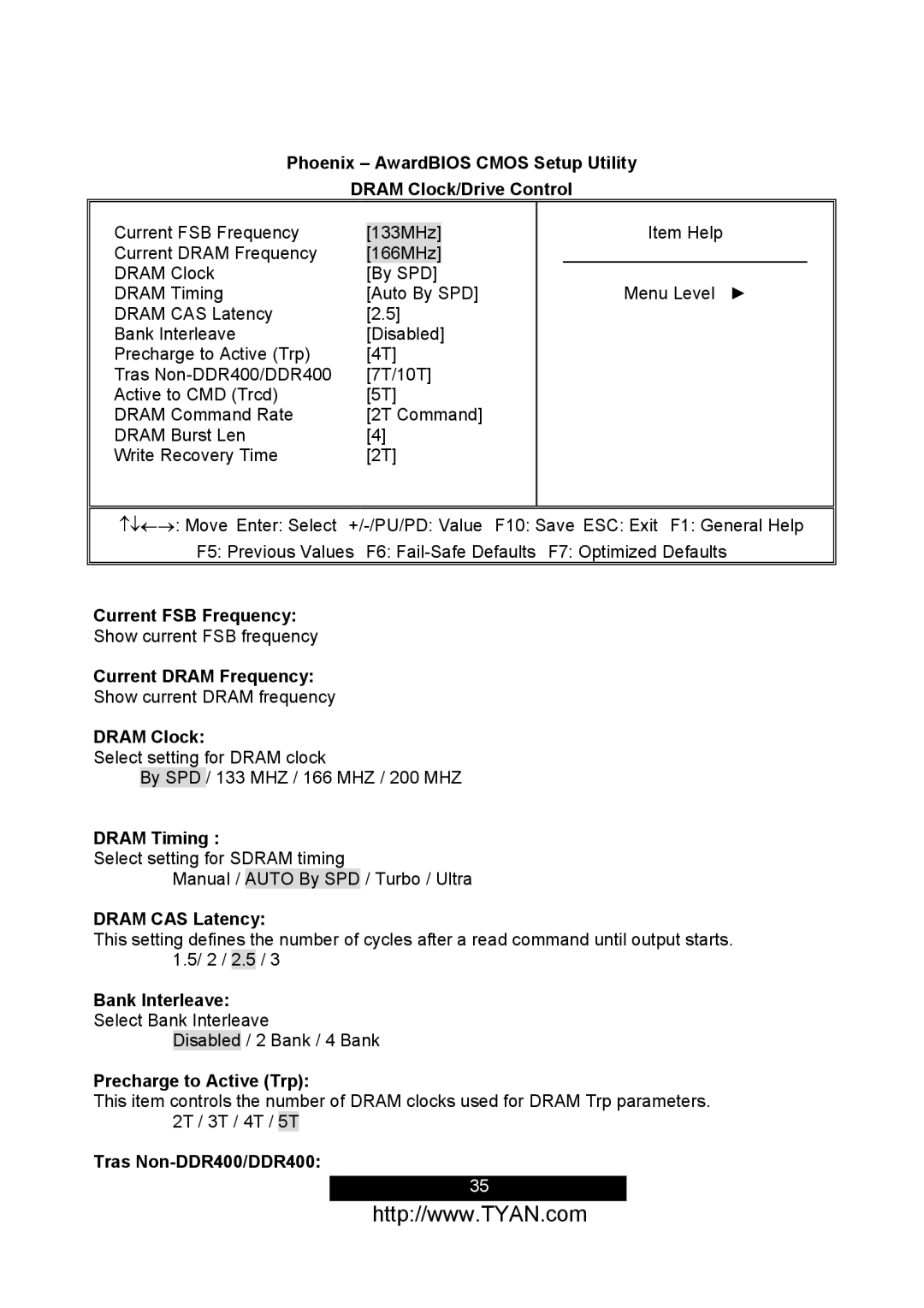

Phoenix – AwardBIOS CMOS Setup Utility

DRAM Clock/Drive Control

|

|

|

|

|

|

Current FSB Frequency |

| [133MHz] |

|

| Item Help |

Current DRAM Frequency |

| [166MHz] |

|

| _________________________ |

DRAM Clock |

| [By SPD] |

|

|

|

DRAM Timing |

| [Auto By SPD] |

| Menu Level ► | |

DRAM CAS Latency | [2.5] |

|

|

| |

Bank Interleave |

| [Disabled] |

|

| |

Precharge to Active (Trp) |

| [4T] |

|

| |

Tras |

| [7T/10T] |

|

| |

Active to CMD (Trcd) |

| [5T] |

|

| |

DRAM Command Rate |

| [2T Command] |

|

| |

DRAM Burst Len | [4] |

|

|

| |

Write Recovery Time |

| [2T] |

|

| |

|

|

|

| ||

↑↓←→: Move Enter: Select | F10: Save ESC: Exit F1: General Help | ||||

F5: Previous Values F6:

Current FSB Frequency:

Show current FSB frequency

Current DRAM Frequency:

Show current DRAM frequency

DRAM Clock:

Select setting for DRAM clock

By SPD / 133 MHZ / 166 MHZ / 200 MHZ

DRAM Timing :

Select setting for SDRAM timing

Manual / AUTO By SPD / Turbo / Ultra

DRAM CAS Latency:

This setting defines the number of cycles after a read command until output starts. 1.5/ 2 / 2.5 / 3

Bank Interleave:

Select Bank Interleave

Disabled / 2 Bank / 4 Bank

Precharge to Active (Trp):

This item controls the number of DRAM clocks used for DRAM Trp parameters. 2T / 3T / 4T / 5T

Tras Non-DDR400/DDR400:

35

http://www.TYAN.com