Simulation

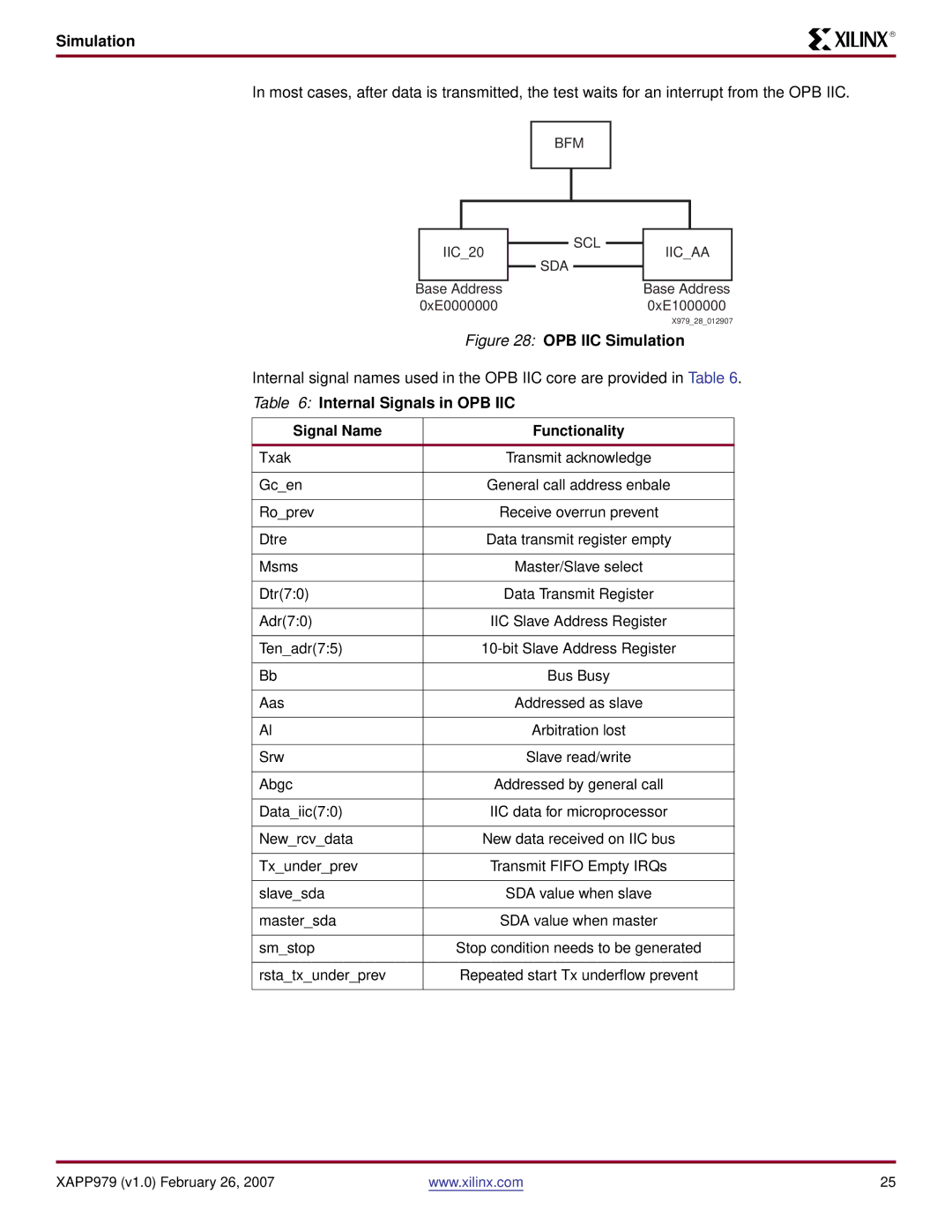

In most cases, after data is transmitted, the test waits for an interrupt from the OPB IIC.

BFM

R

IIC_20

Base Address 0xE0000000

SCL

SDA

IIC_AA

Base Address 0xE1000000

X979_28_012907

Figure 28: OPB IIC Simulation

Internal signal names used in the OPB IIC core are provided in Table 6. Table 6: Internal Signals in OPB IIC

Signal Name | Functionality |

|

|

Txak | Transmit acknowledge |

|

|

Gc_en | General call address enbale |

|

|

Ro_prev | Receive overrun prevent |

|

|

Dtre | Data transmit register empty |

|

|

Msms | Master/Slave select |

|

|

Dtr(7:0) | Data Transmit Register |

|

|

Adr(7:0) | IIC Slave Address Register |

|

|

Ten_adr(7:5) | |

|

|

Bb | Bus Busy |

|

|

Aas | Addressed as slave |

|

|

Al | Arbitration lost |

|

|

Srw | Slave read/write |

|

|

Abgc | Addressed by general call |

|

|

Data_iic(7:0) | IIC data for microprocessor |

|

|

New_rcv_data | New data received on IIC bus |

|

|

Tx_under_prev | Transmit FIFO Empty IRQs |

|

|

slave_sda | SDA value when slave |

|

|

master_sda | SDA value when master |

|

|

sm_stop | Stop condition needs to be generated |

|

|

rsta_tx_under_prev | Repeated start Tx underflow prevent |

|

|

XAPP979 (v1.0) February 26, 2007 | www.xilinx.com | 25 |