Reference System Specifics

R

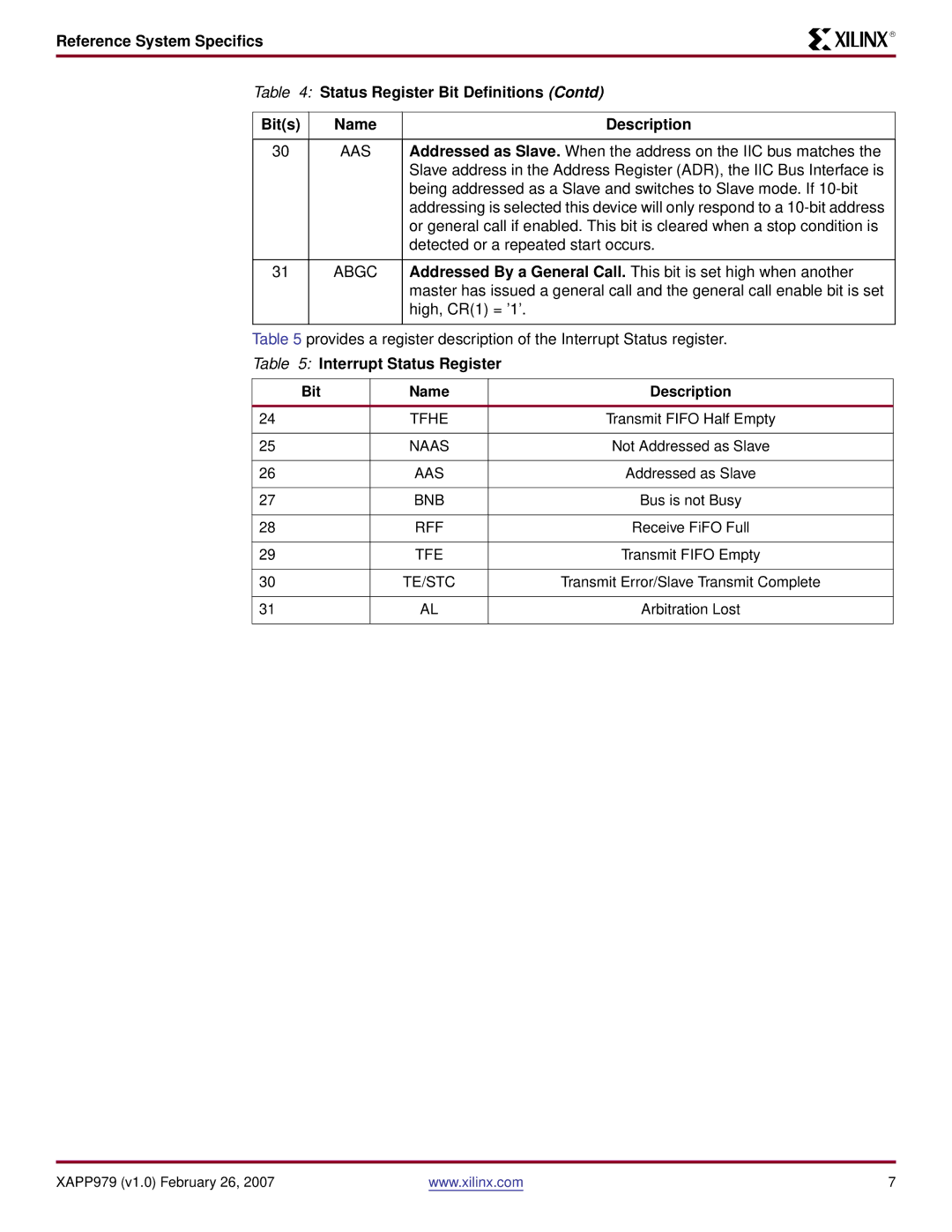

Table 4: | Status Register Bit Definitions (Contd) | ||

|

|

|

|

Bit(s) |

| Name | Description |

|

|

|

|

30 |

| AAS | Addressed as Slave. When the address on the IIC bus matches the |

|

|

| Slave address in the Address Register (ADR), the IIC Bus Interface is |

|

|

| being addressed as a Slave and switches to Slave mode. If |

|

|

| addressing is selected this device will only respond to a |

|

|

| or general call if enabled. This bit is cleared when a stop condition is |

|

|

| detected or a repeated start occurs. |

|

|

|

|

31 |

| ABGC | Addressed By a General Call. This bit is set high when another |

|

|

| master has issued a general call and the general call enable bit is set |

|

|

| high, CR(1) = ’1’. |

|

|

|

|

Table 5 provides a register description of the Interrupt Status register.

Table | 5: Interrupt Status Register |

| ||

|

|

|

|

|

| Bit | Name |

| Description |

|

|

|

|

|

24 |

| TFHE |

| Transmit FIFO Half Empty |

|

|

|

|

|

25 |

| NAAS |

| Not Addressed as Slave |

|

|

|

|

|

26 |

| AAS |

| Addressed as Slave |

|

|

|

|

|

27 |

| BNB |

| Bus is not Busy |

|

|

|

|

|

28 |

| RFF |

| Receive FiFO Full |

|

|

|

|

|

29 |

| TFE |

| Transmit FIFO Empty |

|

|

|

|

|

30 |

| TE/STC |

| Transmit Error/Slave Transmit Complete |

|

|

|

|

|

31 |

| AL |

| Arbitration Lost |

|

|

|

|

|

XAPP979 (v1.0) February 26, 2007 | www.xilinx.com | 7 |