Simulation

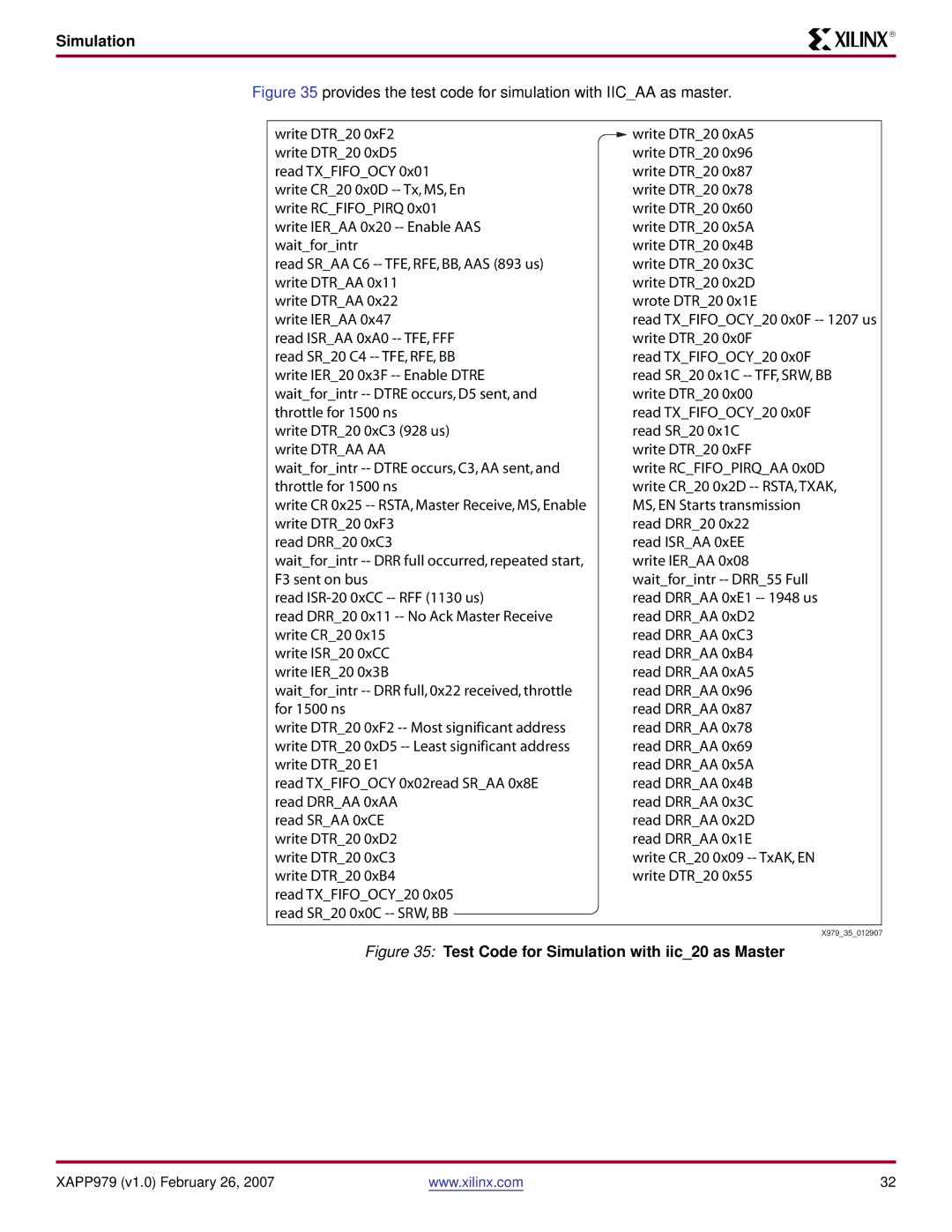

Figure 35 provides the test code for simulation with IIC_AA as master.

R

write DTR_20 0xF2 | write DTR_20 0xA5 |

write DTR_20 0xD5 | write DTR_20 0x96 |

read TX_FIFO_OCY 0x01 | write DTR_20 0x87 |

write CR_20 0x0D | write DTR_20 0x78 |

write RC_FIFO_PIRQ 0x01 | write DTR_20 0x60 |

write IER_AA 0x20 | write DTR_20 0x5A |

wait_for_intr | write DTR_20 0x4B |

read SR_AA C6 | write DTR_20 0x3C |

write DTR_AA 0x11 | write DTR_20 0x2D |

write DTR_AA 0x22 | wrote DTR_20 0x1E |

write IER_AA 0x47 | read TX_FIFO_OCY_20 0x0F |

read ISR_AA 0xA0 | write DTR_20 0x0F |

read SR_20 C4 | read TX_FIFO_OCY_20 0x0F |

write IER_20 0x3F | read SR_20 0x1C |

wait_for_intr | write DTR_20 0x00 |

throttle for 1500 ns | read TX_FIFO_OCY_20 0x0F |

write DTR_20 0xC3 (928 us) | read SR_20 0x1C |

write DTR_AA AA | write DTR_20 0xFF |

wait_for_intr | write RC_FIFO_PIRQ_AA 0x0D |

throttle for 1500 ns | write CR_20 0x2D |

write CR 0x25 | MS, EN Starts transmission |

write DTR_20 0xF3 | read DRR_20 0x22 |

read DRR_20 0xC3 | read ISR_AA 0xEE |

wait_for_intr | write IER_AA 0x08 |

F3 sent on bus | wait_for_intr |

read | read DRR_AA 0xE1 |

read DRR_20 0x11 | read DRR_AA 0xD2 |

write CR_20 0x15 | read DRR_AA 0xC3 |

write ISR_20 0xCC | read DRR_AA 0xB4 |

write IER_20 0x3B | read DRR_AA 0xA5 |

wait_for_intr | read DRR_AA 0x96 |

for 1500 ns | read DRR_AA 0x87 |

write DTR_20 0xF2 | read DRR_AA 0x78 |

write DTR_20 0xD5 | read DRR_AA 0x69 |

write DTR_20 E1 | read DRR_AA 0x5A |

read TX_FIFO_OCY 0x02read SR_AA 0x8E | read DRR_AA 0x4B |

read DRR_AA 0xAA | read DRR_AA 0x3C |

read SR_AA 0xCE | read DRR_AA 0x2D |

write DTR_20 0xD2 | read DRR_AA 0x1E |

write DTR_20 0xC3 | write CR_20 0x09 |

write DTR_20 0xB4 | write DTR_20 0x55 |

read TX_FIFO_OCY_20 0x05 |

|

read SR_20 0x0C |

|

|

|

| X979_35_012907 |

Figure 35: Test Code for Simulation with iic_20 as Master

XAPP979 (v1.0) February 26, 2007 | www.xilinx.com | 32 |