Four delay rate options are 250, 500, 750 and 1000.

!Security Option [Setup]

System | System will not boot and refuses access to Setup page if the cor- |

| rect password is not entered at the prompt. |

Setup | System will boot, but access to Setup requires password (default |

| value). |

!APIC Mode [Enabled]

This item allows user to enabled of disabled “Advanced Programmable Interrupt Controller”. APIC is implemented in the motherboard and must be supported by the operating system, and it extends the number of IRQ's available.

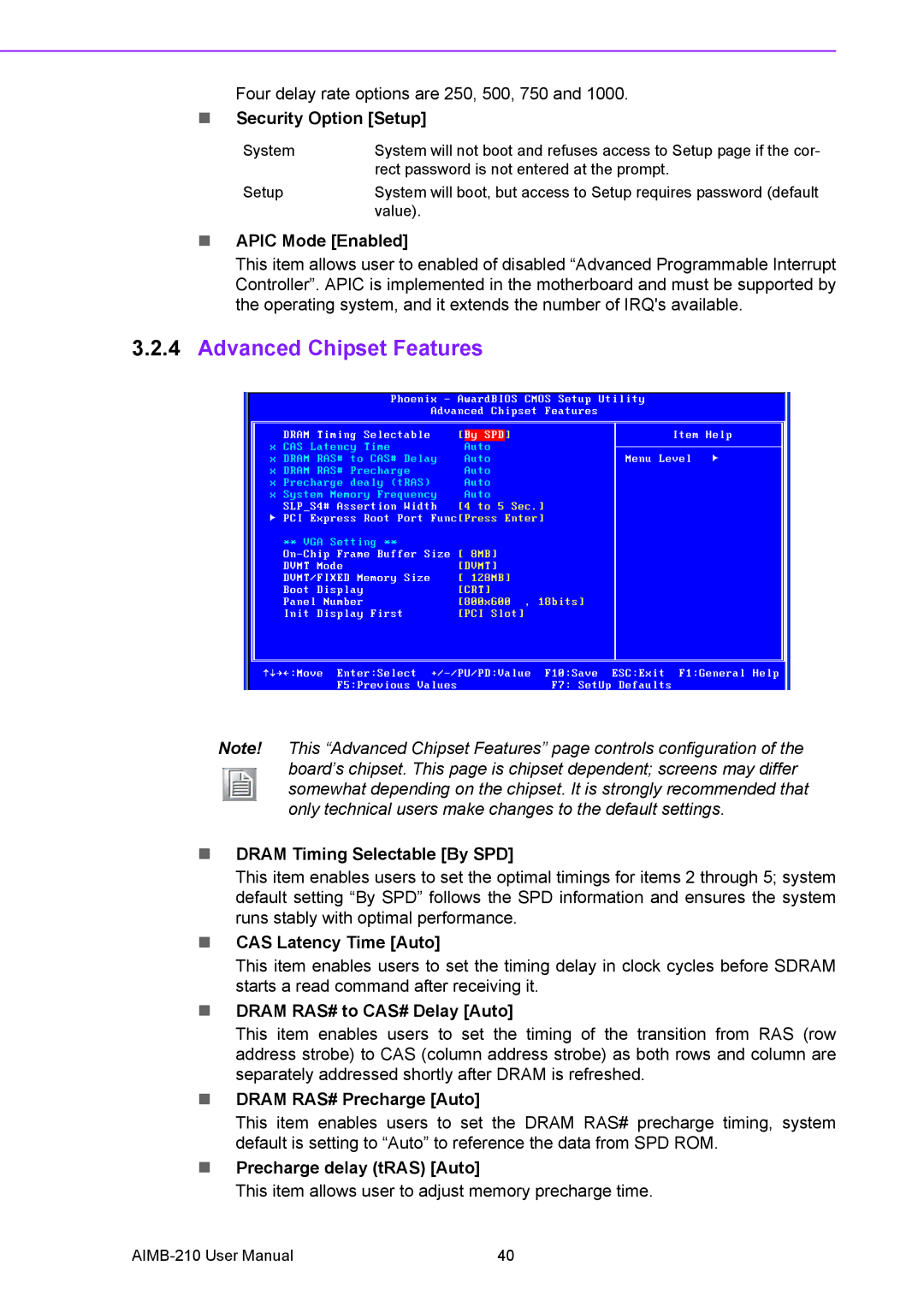

3.2.4Advanced Chipset Features

Note! This “Advanced Chipset Features” page controls configuration of the board’s chipset. This page is chipset dependent; screens may differ somewhat depending on the chipset. It is strongly recommended that only technical users make changes to the default settings.

!DRAM Timing Selectable [By SPD]

This item enables users to set the optimal timings for items 2 through 5; system default setting “By SPD” follows the SPD information and ensures the system runs stably with optimal performance.

!CAS Latency Time [Auto]

This item enables users to set the timing delay in clock cycles before SDRAM starts a read command after receiving it.

!DRAM RAS# to CAS# Delay [Auto]

This item enables users to set the timing of the transition from RAS (row address strobe) to CAS (column address strobe) as both rows and column are separately addressed shortly after DRAM is refreshed.

!DRAM RAS# Precharge [Auto]

This item enables users to set the DRAM RAS# precharge timing, system default is setting to “Auto” to reference the data from SPD ROM.

!Precharge delay (tRAS) [Auto]

This item allows user to adjust memory precharge time.

40 |