‹&RS\ULJKW$JLOHQW7HFKQRORJLHV,QF $OO5LJKWV5HVHUYHG

3DUW1XPEHU $SULO

Flexible system features

Convenient bench-top features

Front Panel at a Glance

Page

T e

Front-Panel Voltage and Current Limit Settings

OVP

Display Annunciators

Key to

Rear Panel at a Glance

This Book

Page

Contents

Contents

Remote Interface Reference

Error Messages

General Information

Safety and EMC Requirements

Safety Considerations

Accessories

Options and Accessories

General Information Options and Accessories

Options

General Information Description

Description

R n i n g

General Information Description R n i n g

Installation

Initial Inspection

Cooling and Location

General Information Installation Rack Mounting

Page

Power-Line Cord

Input Power Requirements

Power-Line Voltage Selection

General Information Input Power Requirements

Panel

Power-line module

General Information Input Power Requirements

Initial Operation

Initial Operation

Verify that the correct power-line fuse is installed

Verify the power-line voltage setting on the rear panel

Connect the power-line cord and turn on your power supply

Preliminary Checkout

Initial Operation Power-On Checkout

Enable the outputs

Addr 05 or RS-232

Output Checkout

Voltage Output Checkout

Initial Operation Output Checkout

Turn on the power supply

Adjust the voltage limit value to 1.0 volt

Current Output Checkout

T e

Initial Operation Output Checkout

Front-Panel Operation

Front-Panel Operation

Front-Panel Operation Front-Panel Operation Overview

Front-Panel Operation Overview

Adjust the knob for the desired current limit

Set the display to the limit mode

Constant Voltage Operation

Front-Panel Operation Constant Voltage Operation

CURRent currentMINMAX

Return to the meter mode

VOLTage voltageMINMAX

OUTPut on

Adjust the knob for the desired voltage limit

Constant Current Operation

Front-Panel Operation Constant Current Operation

Verify that the power supply is in the constant current mode

Turn on the storage mode

Set up the power supply for the desired operating state

Storing and Recalling Operating States

Store the operating state in memory location

RCL

SAV

Setting the OVP Level and Enable the OVP Circuit

Programming Overvoltage Protection

Level 32.0

Move to the clear mode Ovp on

Readjust the OVP trip level or the output voltage level

Checking OVP Operation

Clearing the Overvoltage Condition

Voltprot voltageMINMAX

Clear the overvoltage condition and exit this menu

Voltprotstat Offon

Voltprotcle

Enable the OCP circuit

Setting the OCP Level and Enable the OCP Circuit

Programming Overcurrent Protection

Front-Panel Operation Programming Overcurrent Protection

Move to the clear mode Ocp on

Readjust the OCP trip level or the output current level

Checking OCP Operation

Clearing the Overcurrent Condition

Currprot currentMINMAX

Clear the overcurrent condition and exit this menu

Currprotstat Offon

Currprotcle

CV Regulation

Remote Voltage Sensing

Output Rating

Output Noise

Remote Voltage Sensing Connections

Stability

Disabling the Output

Front-Panel Operation Disabling the Output

Outp Offon

Knob Locking

Disabling the Output Using an External Relay

Self-Test

System-Related Operations

Front-Panel Operation System-Related Operations

TST?

ERR

Error Conditions

SYSTERR?

113, Undefined header

Disp Offon

Display Control

Disptextcle

Disptext ‘HELLO’

Scpi Language Version

Firmware Revision Query

IDN? Returns HEWLETT-PACKARD,E3632A,0,X.X-X.X-X.X

SYSTVERS?

Remote Interface Configuration

Front-Panel Operation Remote Interface Configuration

Remote Interface Selection

Gpib Address

Baud Rate Selection RS-232

Parity Selection RS-232

Gpib

To Set the Gpib Address

RS-232

To Set the Baud Rate and Parity RS-232

Baud

Choose the RS-232 interface

For one second

T e Front-Panel Operation Gpib Interface Configuration

Gpib Interface Configuration

RS-232 Configuration Overview

RS-232 Interface Configuration

Front-Panel Operation RS-232 Interface Configuration

RS-232 Data Frame Format

Connection to a Computer or Terminal

DTR / DSR Handshake Protocol

RS-232 Troubleshooting

Calibration Overview

Calibration Security

Front-Panel Operation Calibration Overview

Calsecstat OFF, HP003632

Code

Calsecstat ON, HP003632

ZZ001443

Calseccode

Calsecstat

ON, ZZ00143

Calibration Count

Calibration Message

Calstr ‘CAL 05-1-97’

Remote Interface Reference

Scpi

Remote Interface Reference Scpi Command Summary

Scpi Command Summary

VOLTageDC?

System-Related Commands

Status Reporting Commands

IEEE-488.2 Common Commands

Using the Low-Level Commands

Using the APPLy Command

Simplified Programming Overview

‘‘VOLT

Selecting a Trigger Source

Reading a Query Response

‘‘SYSTERR?’’

‘‘TRIGSOUR IMM’’

3RZHU6XSSO\3URJUDPPLQJ5DQJHV

Remote Interface Reference Using the APPLy Command

Using the APPLy Command

APPLy voltage DEF MIN MAX,current DEF MIN MAX

APPLy?

Output Setting and Operation Commands

Curr UP

Curr Down

CURRentSTEP? DEFault

CURRentSTEP numeric valueDEFault

CURRentTRIGgered current MINimum MAXimum

CURRentTRIGgered? MINimum MAXimum

CURRentPROTectionSTATe 01OFFON

CURRentPROTection? MINimumMAXimum

CURRentPROTectionSTATe?

CURRentPROTectionTRIPped?

Volt Down

Volt UP

VOLTageTRIGgered voltage MINimum MAXimum

VOLTageSTEP? DEFault

VOLTageTRIGgered? MINimum MAXimum

VOLTagePROTection voltageMINimumMAXimum

VOLTagePROTectionSTATe?

VOLTagePROTectionSTATe 01OFFON

VOLTagePROTectionTRIPped?

VOLTagePROTectionCLEar

MEASureVOLTage?

Remote Interface Reference Triggering Commands

Triggering Commands

Trigger Source Choices

Bus Software Triggering

Trigsour BUS*TRG*WAI*TRG*WAI

Trigger 705 group execute trigger

Immediate Triggering

Trigsour IMM

TRG

Triggering Commands

System-Related Commands

SYSTemERRor?

OUTPutRELay?

SYSTemBEEPer

HEWLETT-PACKARD,E3632A,0,X.X-X.X-X.X RST

IDN?

Curr Currstep

Currtrig Currprot Currprotstat Disp Outp

RCL 1 2

SAV 1 2

Calibration Commands

CALibrationSECureSTATe OFF ON,code

CALibrationSECureCODE new code

CALibrationSECureSTATe?

CALibrationSTRing quoted string

CALibrationVOLTagePROTection

RS-232 Interface Commands

What is an Enable Register?

What is an Event Register?

Scpi Status Registers

Remote Interface Reference Scpi Status Registers

101

Scpi Status System

Questionable Status Register

Questionable Status Enable register is cleared when

Questionable Status Event register is cleared when

102

103

Standard Event Register

Standard Event Enable register is cleared when

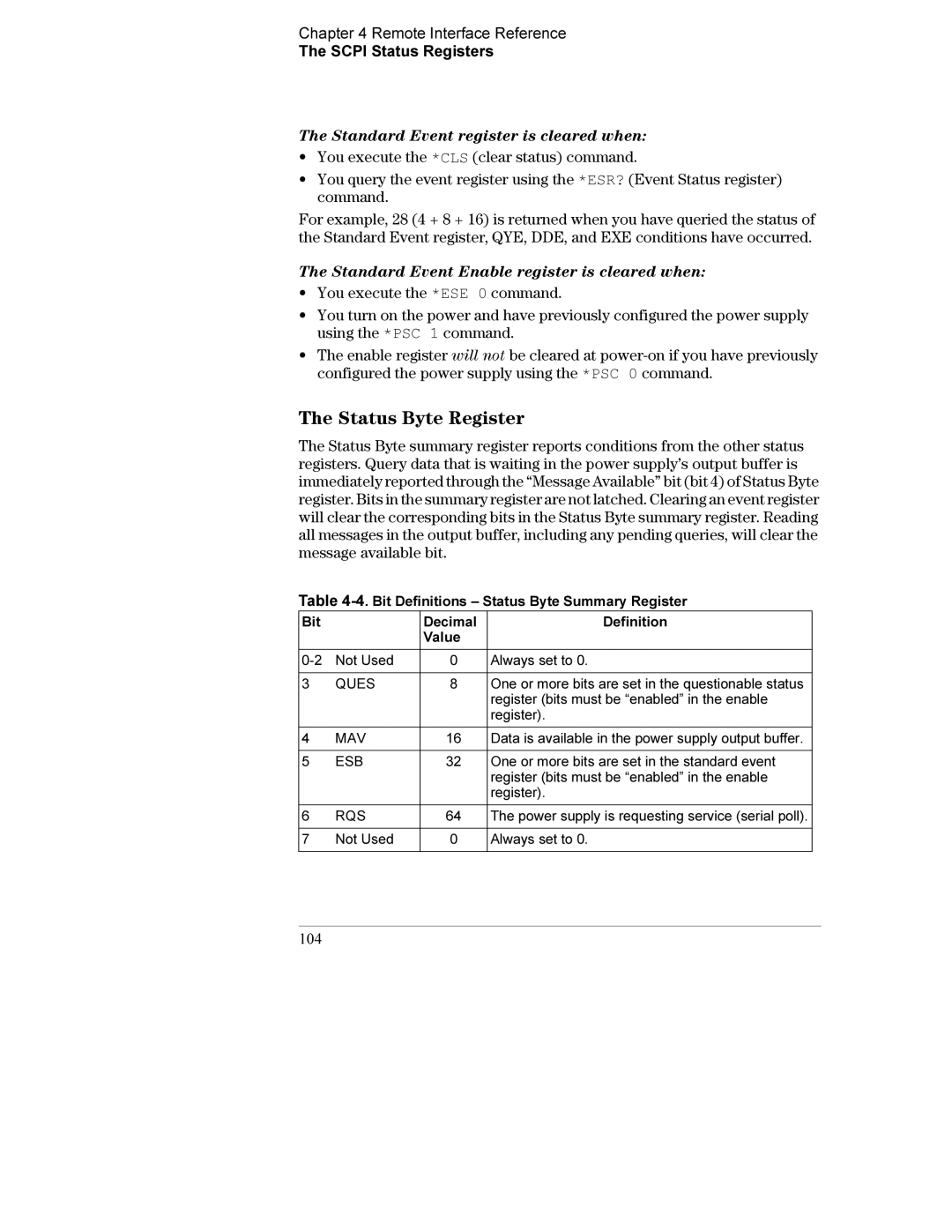

Status Byte Register

104

‡ RXHHFXWHWKH*CLSFOHDUVWDWXVFRPPDQG

‡ RXHHFXWHWKH*SRE 0FRPPDQG

Diihfwlqvwuxphqwwkurxjksxw

Using *STB? to Read the Status Byte

Using the Message Available Bit MAV

To Interrupt Your Bus Controller Using SRQ

To Determine When a Command Sequence is Completed

Using *OPC to Signal When Data is in the Output Buffer

107

Remote Interface Reference Status Reporting Commands

Status Reporting Commands

STATusQUEStionableCONDition?

STATusQUEStionable?

ESE?

CLS

ESR?

OPC

SRE?

PSC?

STB?

WAI

111

An Introduction to the Scpi Language

Command Format Used in This Manual

CURRent currentMINimumMAXimumUPDOWN

‘‘SOURceCURRentTRIGgered’’ ‘‘APPLy 3.5,1.5’’ 112

Using the MIN and MAX Parameters

Command Separators

Sourvolt Mincurr MAX

Sourvolt MIN Sourcurr MAX

Scpi Command Terminators

Querying Parameter Settings

IEEE-488.2 Common Commands

‘‘CURR? MAX’’

Curr currentMINMAXUPDOWN

Scpi Parameter Types

Trigsour Busimm

115

‡ 7KHSRZHUVXSSO\ªVLQSXWDQGRXWSXWEXIIHUVDUHFOHDUHG

Halting an Output in Progress

RQILUPHG&RPPDQGV

Scpi Conformance Information

SOURce VOLTageLEVelIMMediateAMPLitude voltageMINMAXUPDOWN

118

HYLFH6SHFLILF&RPPDQGV

IEEE-488 Conformance Information

Error Messages

113, Undefined header 122

Error

Appl

Execution Errors

Undefined header

Program mnemonic too long

Example Triggdel

Invalid character in number

Expression errors

Block data errors

Invalid character data

Character data too long

CALibrationSTRing command

Settings conflict

Too many errors

Data out of range

Isolator Uart overrun error

Isolator Uart framing error

RS-232 framing error

RS-232 overrun error

Self-Test Errors

Calibration Errors

Cal OVP or OCP status enabled

Bad DAC DNL error correction data

Cal checksum failed, DAC DNL error correction data

Bad OVP cal data

Application Programs

132

Application Programs C++ Example for Gpibieee

++ Example for Gpibieee

Diode.c

133

End of Program 134

Application Programs ++ Example for Gpibieee

135

Excel 5.0 Example for Windows 3.1 and Gpib

136

Visuccess

137

End of Program 138

Tutorial

140

Overview of Agilent E3632A Operation

Tutorial Overview of Agilent E3632A Operation

141

142

Output Characteristics

Tutorial Output Characteristics

143

144

Output Characteristics

Unwanted Signals

Unregulated State

145

146

Tutorial Connecting the Load

Connecting the Load

Output Isolation

Multiple Loads

Tutorial Connecting the Load R n i n g

Remote Voltage Sensing

148

Capacitive Loading

Load Consideration

Inductive loading

Pulse Loading

150

Tutorial Connecting the Load Reverse Current Loading

Series Connections

Extending the Voltage and Current Range

Parallel Connections

Tutorial Extending the Voltage and Current Range

Remote Programming

Tutorial Remote Programming

152

Speed of Response Programming Down

153

Reliability

Tutorial Reliability

154

Specifications

156

Performance Specifications

Specifications Performance Specifications

157

OCP

158

Supplemental Characteristics

Specifications Supplemental Characteristics

159

160

161

Dimensions of Agilent E3632A Power Supply

Specifications Supplemental Characteristics 162

163

Index

164

165

166

Warranty

According to ISO/IEC Guide 22 and EN

Declaration of Conformity