31994A | AMD Sempron™ Processor Model 10 with 256K L2 Cache Data Sheet |

4 Power Management

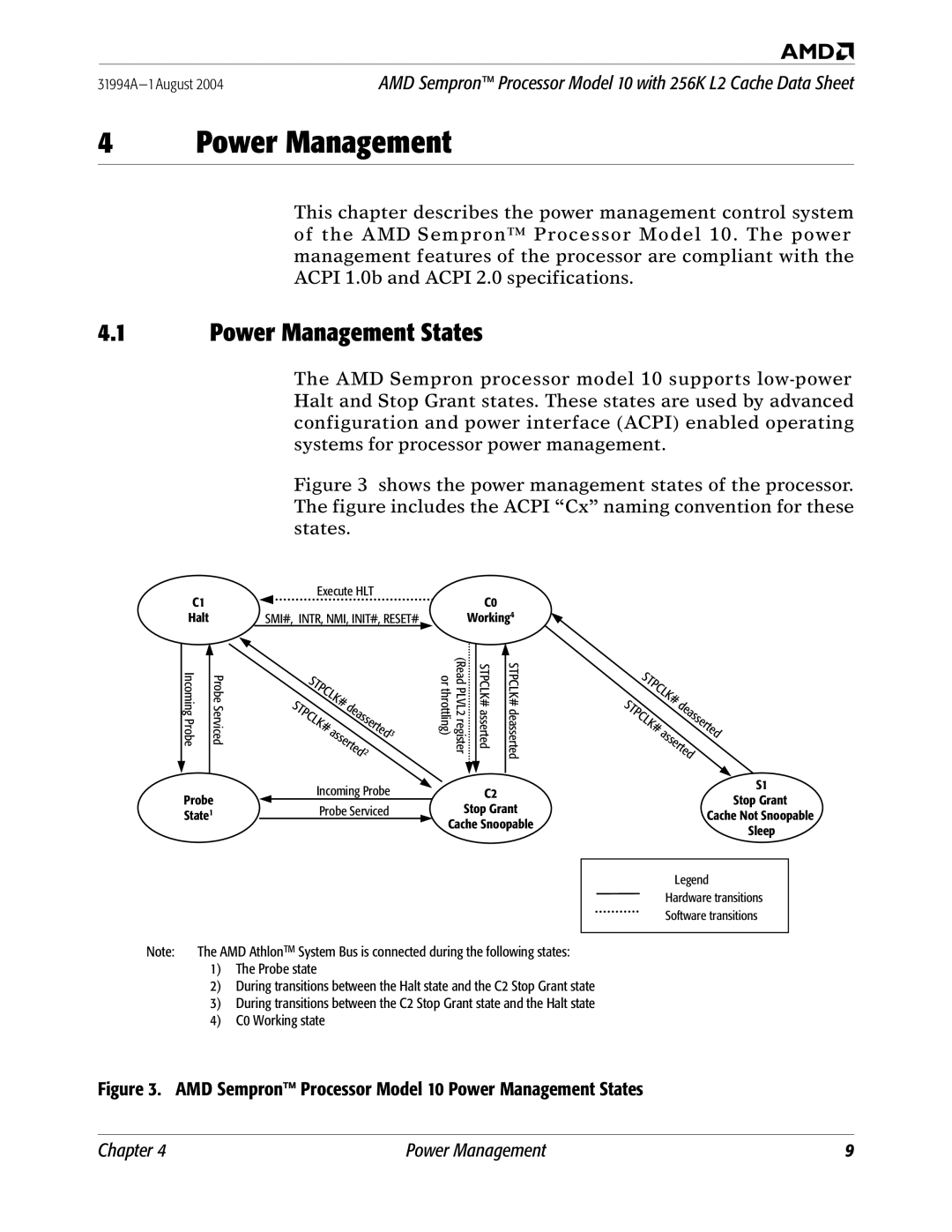

This chapter describes the power management control system of the AMD Sempron™ Processor Model 10. The power management features of the processor are compliant with the ACPI 1.0b and ACPI 2.0 specifications.

4.1Power Management States

The AMD Sempron processor model 10 supports

Figure 3 shows the power management states of the processor. The figure includes the ACPI “Cx” naming convention for these states.

C1 |

|

|

|

|

|

| Execute HLT |

|

|

|

|

|

| C0 |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Halt |

|

| SMI#, INTR, NMI, INIT#, RESET# |

|

|

| Working4 | |||||||||||||||||||

IncomingProbe |

| P |

|

|

| S |

|

|

|

|

|

|

|

|

|

|

|

| orthrottling) | (ReadPLVL2register |

| STPCLK#asserted |

| STPCLK#deasserted | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

| r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| o |

|

|

|

| T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| b |

|

|

|

|

|

|

| C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| e |

|

|

|

|

|

|

|

| K |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| S |

|

| S |

|

|

|

|

|

| # |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| d |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| e |

|

| P |

|

|

|

|

|

| e |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| r |

|

|

| C |

|

|

|

|

|

|

| s |

|

|

|

|

|

|

|

|

|

| ||

|

| v |

|

|

|

| L |

|

|

|

|

|

|

| s |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| K |

|

|

|

|

| e |

|

|

|

|

|

|

|

|

| ||||

|

| i |

|

|

|

|

|

| # |

|

|

|

|

|

| r |

|

|

|

|

|

|

|

| ||

|

| c |

|

|

|

|

|

|

|

|

|

|

|

|

| t |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| a |

|

|

|

|

| e |

|

|

|

|

|

|

| ||||

|

| e |

|

|

|

|

|

|

|

|

|

|

|

|

| d3 |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| s |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| d |

|

|

|

|

|

|

|

|

| s |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| e |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| e |

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| d2 |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| Incoming Probe |

|

|

|

| C2 |

|

| |||||||||||

Probe |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

| Probe Serviced |

|

| Stop Grant | ||||||||||||||||

State1 |

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Cache Snoopable | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

Note: | The AMD AthlonTM System Bus is connected during the following states: |

1)The Probe state

2)During transitions between the Halt state and the C2 Stop Grant state

3)During transitions between the C2 Stop Grant state and the Halt state

4)C0 Working state

| S |

|

|

|

| T |

|

|

|

| P |

|

|

|

| C |

|

|

|

| L |

|

|

|

| K |

|

| |

S | # |

|

| |

| d |

|

| |

T | e |

|

| |

P | a |

|

| |

| C | s | ||

| L | s | ||

| K |

| e | |

|

| r | ||

| # |

| t | |

|

| e | ||

| a |

| d | |

| s |

|

| |

| s |

|

| |

|

| e |

|

|

|

| r |

|

|

|

| t |

|

|

|

| e |

|

|

|

| d |

|

|

|

|

| S1 | |

|

|

| Stop Grant | |

|

|

| Cache Not Snoopable | |

|

|

| Sleep | |

|

|

| ||

|

| Legend |

| |

| Hardware transitions |

| ||

| Software transitions |

| ||

|

|

|

|

|

Figure 3. AMD Sempron™ Processor Model 10 Power Management States

Chapter 4 | Power Management | 9 |