AMD Sempron™ Processor Model 10 with 256K L2 Cache Data Sheet |

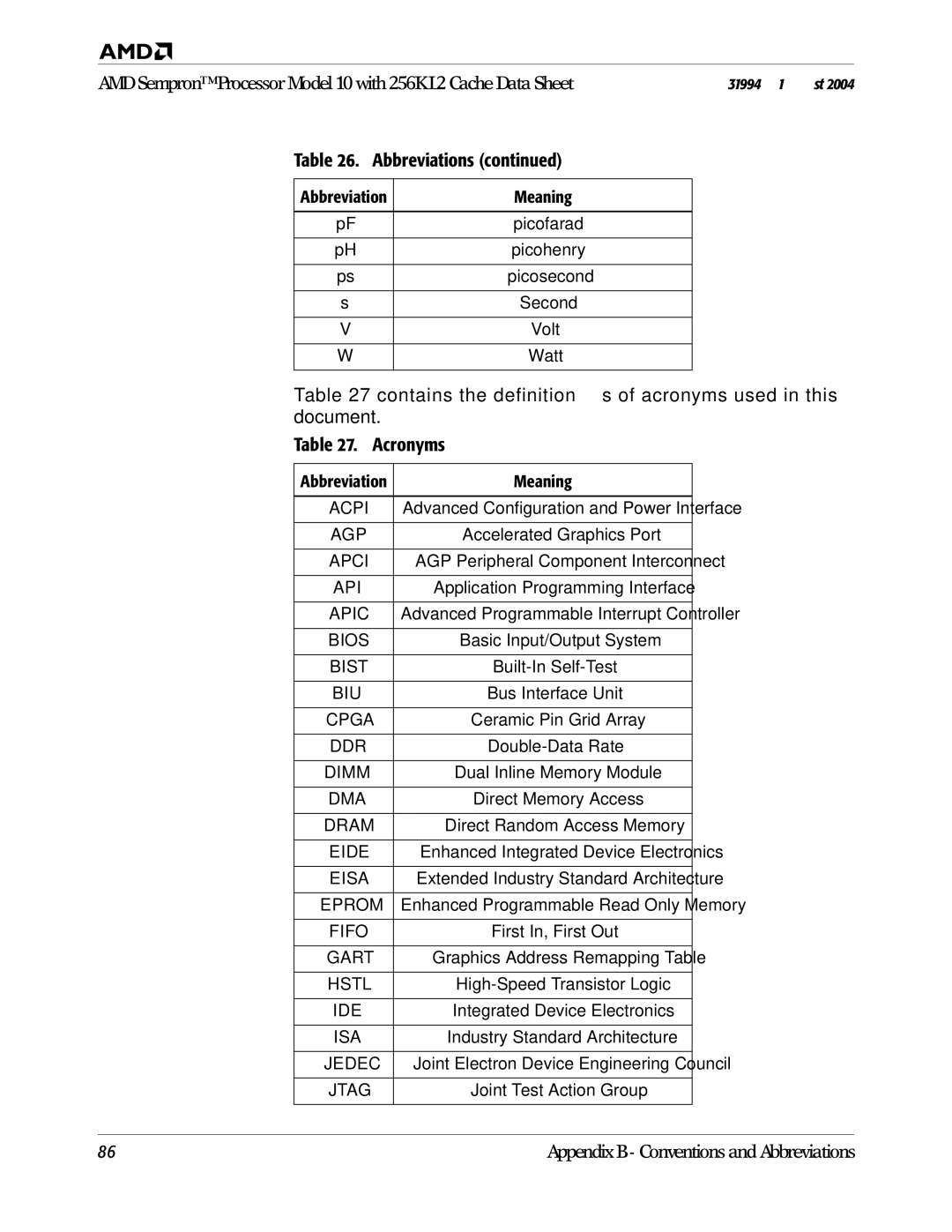

| Table 26. | Abbreviations (continued) | ||

|

|

|

| |

| Abbreviation | Meaning |

| |

|

|

|

|

|

| pF |

| picofarad |

|

|

|

|

|

|

| pH |

| picohenry |

|

|

|

|

|

|

| ps |

| picosecond |

|

|

|

|

|

|

| s |

| Second |

|

|

|

|

|

|

| V |

| Volt |

|

|

|

|

|

|

| W |

| Watt |

|

|

|

|

| |

| Table 27 contains the definitions of acronyms used in this | |||

| document. |

|

| |

| Table 27. | Acronyms | ||

|

|

|

| |

| Abbreviation | Meaning |

| |

|

|

|

|

|

| ACPI |

| Advanced Configuration and Power Interface |

|

|

|

|

|

|

| AGP |

| Accelerated Graphics Port |

|

|

|

|

|

|

| APCI |

| AGP Peripheral Component Interconnect |

|

|

|

|

|

|

| API |

| Application Programming Interface |

|

|

|

|

|

|

| APIC |

| Advanced Programmable Interrupt Controller |

|

|

|

|

|

|

| BIOS |

| Basic Input/Output System |

|

|

|

|

|

|

| BIST |

|

| |

|

|

|

|

|

| BIU |

| Bus Interface Unit |

|

|

|

|

|

|

| CPGA |

| Ceramic Pin Grid Array |

|

|

|

|

|

|

| DDR |

|

| |

|

|

|

|

|

| DIMM |

| Dual Inline Memory Module |

|

|

|

|

|

|

| DMA |

| Direct Memory Access |

|

|

|

|

|

|

| DRAM |

| Direct Random Access Memory |

|

|

|

|

|

|

| EIDE |

| Enhanced Integrated Device Electronics |

|

|

|

|

|

|

| EISA |

| Extended Industry Standard Architecture |

|

|

|

|

|

|

| EPROM |

| Enhanced Programmable Read Only Memory |

|

|

|

|

|

|

| FIFO |

| First In, First Out |

|

|

|

|

|

|

| GART |

| Graphics Address Remapping Table |

|

|

|

|

|

|

| HSTL |

|

| |

|

|

|

|

|

| IDE |

| Integrated Device Electronics |

|

|

|

|

|

|

| ISA |

| Industry Standard Architecture |

|

|

|

|

|

|

| JEDEC |

| Joint Electron Device Engineering Council |

|

|

|

|

|

|

| JTAG |

| Joint Test Action Group |

|

|

|

|

|

|

|

|

|

|

|

86 |

|

| Appendix B - Conventions and Abbreviations | |