31994A | AMD Sempron™ Processor Model 10 with 256K L2 Cache Data Sheet |

signals High above 2.5 V. Do not expose these pins to a differential voltage greater than 1.60 V, relative to the processor core voltage.

Refer to “VCC_2.5V Generation Circuit” found in the section, “Motherboard Required Circuits,” of the AMD Athlon™ Processor Motherboard Design Guide, order# 24363 for the required supporting circuitry.

See “Frequency Identification (FID[3:0])” on page 27 for the

DC characteristics for FID[3:0].

FSB_Sense[1:0] Pins FSB_Sense[1:0] pins are either open circuit (logic level of 1) or are pulled to ground (logic level of 0) on the processor package with a 1 kΩ resistor. In conjunction with a circuit on the motherboard, these pins may be used to automatically detect the

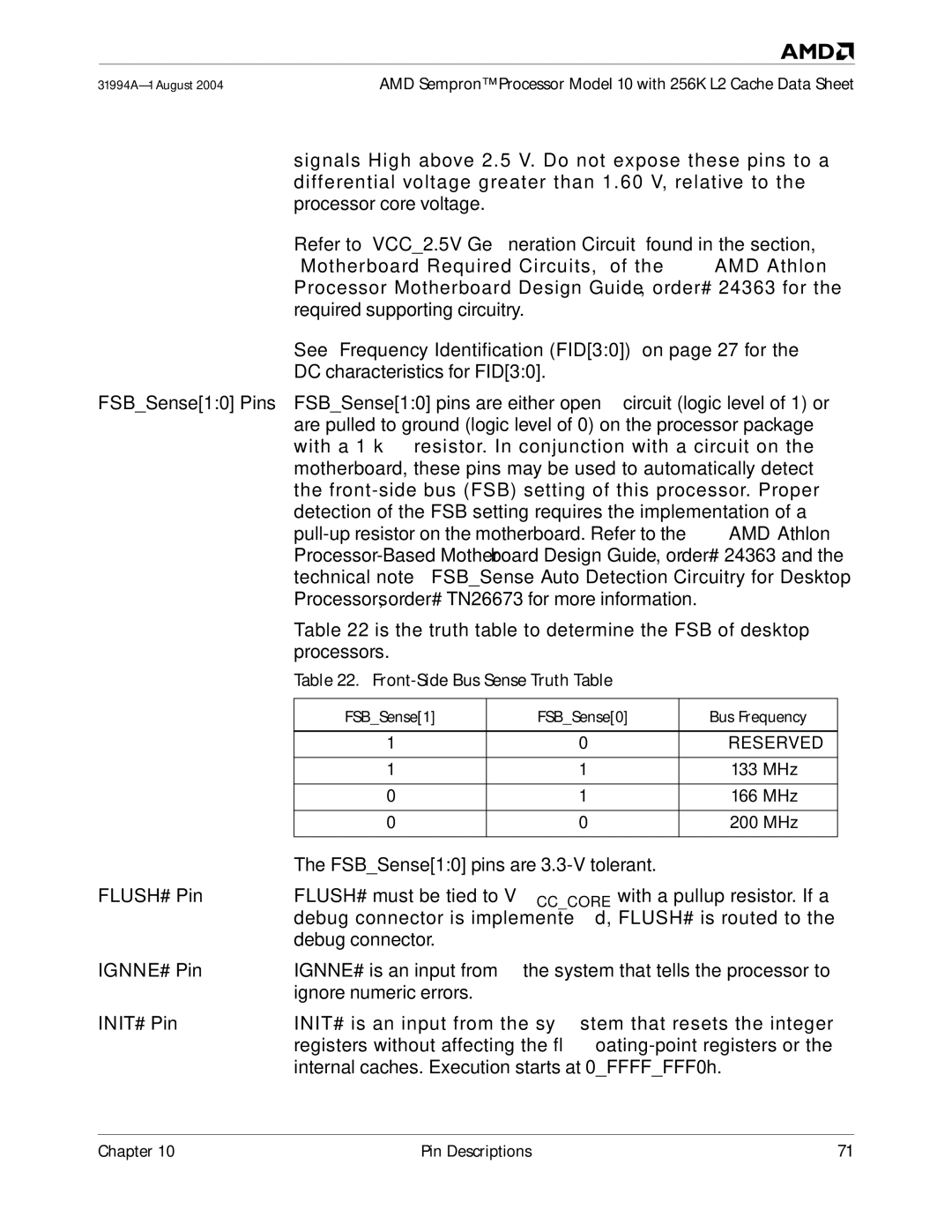

Table 22 is the truth table to determine the FSB of desktop processors.

Table 22. Front-Side Bus Sense Truth Table

FSB_Sense[1] | FSB_Sense[0] | Bus Frequency |

|

|

|

1 | 0 | RESERVED |

|

|

|

1 | 1 | 133 MHz |

|

|

|

0 | 1 | 166 MHz |

|

|

|

0 | 0 | 200 MHz |

|

|

|

| The FSB_Sense[1:0] pins are |

FLUSH# Pin | FLUSH# must be tied to VCC_CORE with a pullup resistor. If a |

| debug connector is implemented, FLUSH# is routed to the |

| debug connector. |

IGNNE# Pin | IGNNE# is an input from the system that tells the processor to |

| ignore numeric errors. |

INIT# Pin | INIT# is an input from the system that resets the integer |

| registers without affecting the |

| internal caches. Execution starts at 0_FFFF_FFF0h. |

Chapter 10 | Pin Descriptions | 71 |