AMD Sempron™ Processor Model 10 with 256K L2 Cache Data Sheet |

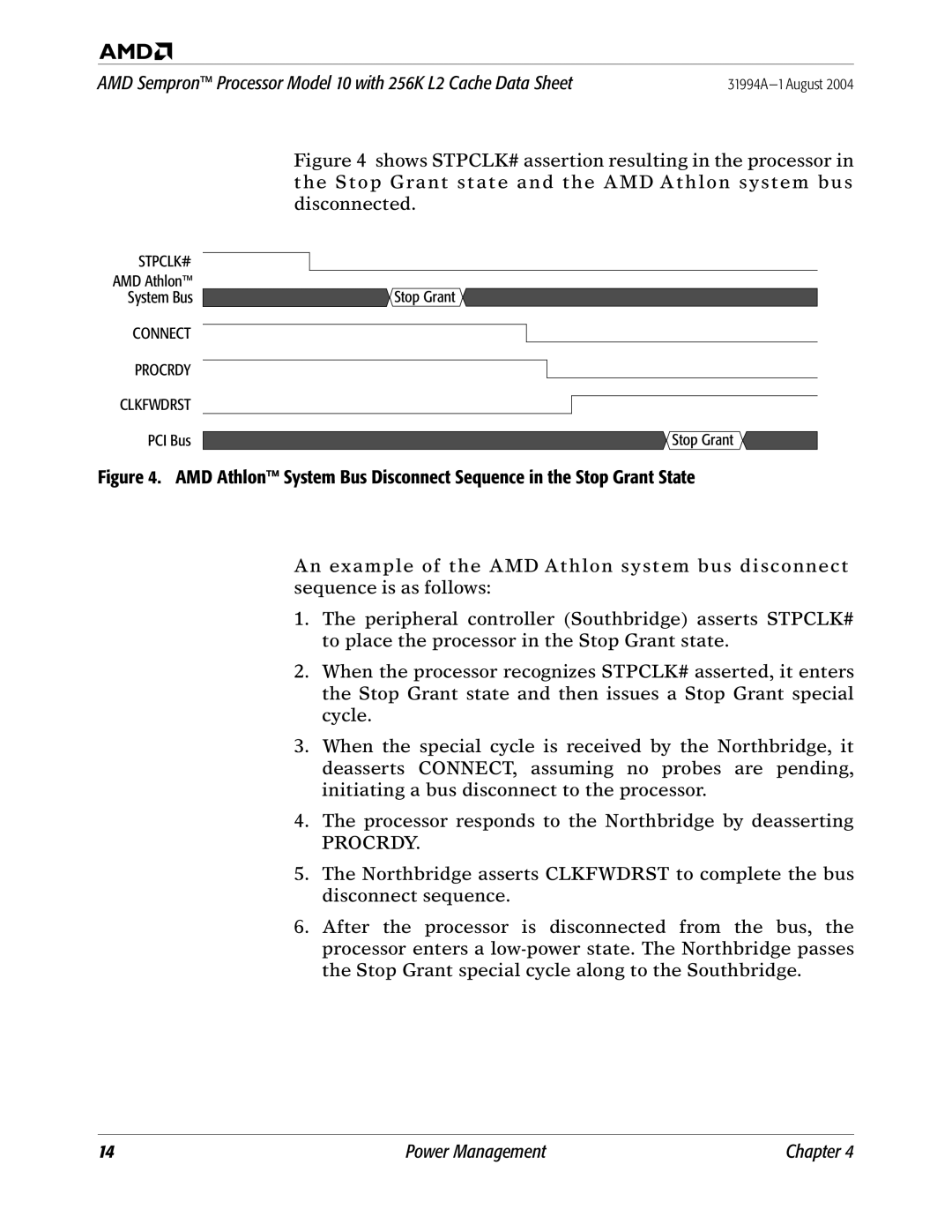

Figure 4 shows STPCLK# assertion resulting in the processor in the Stop Grant state and the AMD Athlon system bus disconnected.

STPCLK#

AMD Athlon™

System Bus ![]() Stop Grant

Stop Grant ![]()

CONNECT

PROCRDY

CLKFWDRST

PCI Bus ![]() Stop Grant

Stop Grant

Figure 4. AMD Athlon™ System Bus Disconnect Sequence in the Stop Grant State

An example of the AMD Athlon system bus disconnect sequence is as follows:

1.The peripheral controller (Southbridge) asserts STPCLK# to place the processor in the Stop Grant state.

2.When the processor recognizes STPCLK# asserted, it enters the Stop Grant state and then issues a Stop Grant special cycle.

3.When the special cycle is received by the Northbridge, it deasserts CONNECT, assuming no probes are pending, initiating a bus disconnect to the processor.

4.The processor responds to the Northbridge by deasserting

PROCRDY.

5.The Northbridge asserts CLKFWDRST to complete the bus disconnect sequence.

6.After the processor is disconnected from the bus, the processor enters a

14 | Power Management | Chapter 4 |