|

|

|

| CY7C1386DV25, CY7C1386FV25 |

|

|

|

| CY7C1387DV25, CY7C1387FV25 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

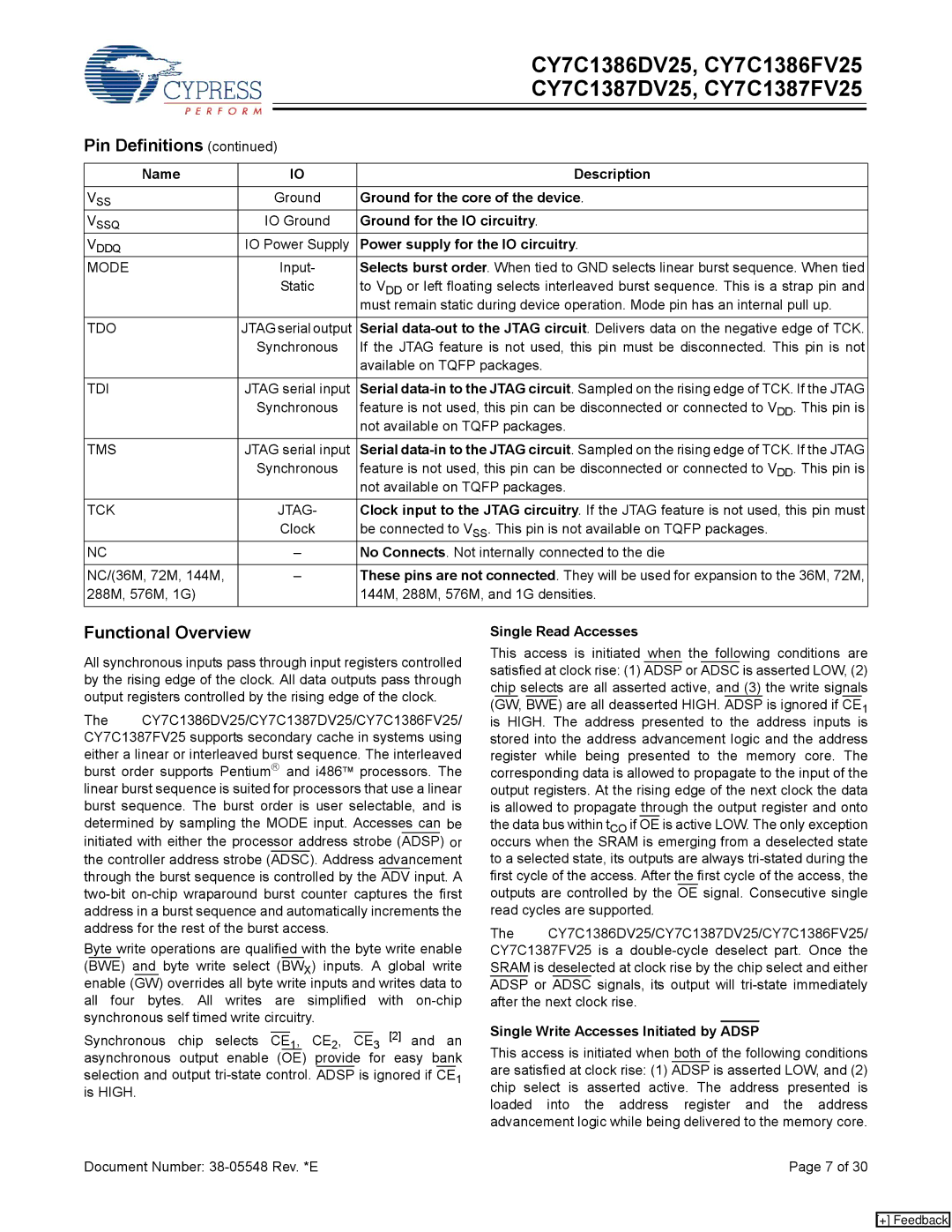

Pin Definitions (continued) |

| |||

|

|

|

|

|

Name |

|

| IO | Description |

|

|

|

|

|

VSS |

|

| Ground | Ground for the core of the device. |

VSSQ |

| IO Ground | Ground for the IO circuitry. | |

VDDQ | IO Power Supply | Power supply for the IO circuitry. | ||

MODE |

|

| Input- | Selects burst order. When tied to GND selects linear burst sequence. When tied |

|

|

| Static | to VDD or left floating selects interleaved burst sequence. This is a strap pin and |

|

|

|

| must remain static during device operation. Mode pin has an internal pull up. |

|

|

| ||

TDO | JTAG serial output | Serial | ||

| Synchronous | If the JTAG feature is not used, this pin must be disconnected. This pin is not | ||

|

|

|

| available on TQFP packages. |

|

|

| ||

TDI | JTAG serial input | Serial | ||

| Synchronous | feature is not used, this pin can be disconnected or connected to VDD. This pin is | ||

|

|

|

| not available on TQFP packages. |

|

|

| ||

TMS | JTAG serial input | Serial | ||

| Synchronous | feature is not used, this pin can be disconnected or connected to VDD. This pin is | ||

|

|

|

| not available on TQFP packages. |

|

|

|

|

|

TCK |

|

| JTAG- | Clock input to the JTAG circuitry. If the JTAG feature is not used, this pin must |

|

|

| Clock | be connected to VSS. This pin is not available on TQFP packages. |

NC |

|

| – | No Connects. Not internally connected to the die |

|

|

|

|

|

NC/(36M, 72M, 144M, |

|

| – | These pins are not connected. They will be used for expansion to the 36M, 72M, |

288M, 576M, 1G) |

|

|

| 144M, 288M, 576M, and 1G densities. |

|

|

|

|

|

Functional Overview

All synchronous inputs pass through input registers controlled by the rising edge of the clock. All data outputs pass through output registers controlled by the rising edge of the clock.

The CY7C1386DV25/CY7C1387DV25/CY7C1386FV25/ CY7C1387FV25 supports secondary cache in systems using either a linear or interleaved burst sequence. The interleaved burst order supports Pentium® and i486™ processors. The linear burst sequence is suited for processors that use a linear burst sequence. The burst order is user selectable, and is determined by sampling the MODE input. Accesses can be initiated with either the processor address strobe (ADSP) or the controller address strobe (ADSC). Address advancement through the burst sequence is controlled by the ADV input. A

Byte write operations are qualified with the byte write enable (BWE) and byte write select (BWX) inputs. A global write enable (GW) overrides all byte write inputs and writes data to all four bytes. All writes are simplified with

Synchronous chip selects CE1, CE2, CE3 [2] and an asynchronous output enable (OE) provide for easy bank selection and output

Single Read Accesses

This access is initiated when the following conditions are satisfied at clock rise: (1) ADSP or ADSC is asserted LOW, (2) chip selects are all asserted active, and (3) the write signals (GW, BWE) are all deasserted HIGH. ADSP is ignored if CE1 is HIGH. The address presented to the address inputs is stored into the address advancement logic and the address register while being presented to the memory core. The corresponding data is allowed to propagate to the input of the output registers. At the rising edge of the next clock the data is allowed to propagate through the output register and onto the data bus within tCO if OE is active LOW. The only exception occurs when the SRAM is emerging from a deselected state to a selected state, its outputs are always

The CY7C1386DV25/CY7C1387DV25/CY7C1386FV25/ CY7C1387FV25 is a

Single Write Accesses Initiated by ADSP

This access is initiated when both of the following conditions are satisfied at clock rise: (1) ADSP is asserted LOW, and (2) chip select is asserted active. The address presented is loaded into the address register and the address advancement logic while being delivered to the memory core.

Document Number: | Page 7 of 30 |

[+] Feedback