CY8C20x36/46/66, CY8C20396

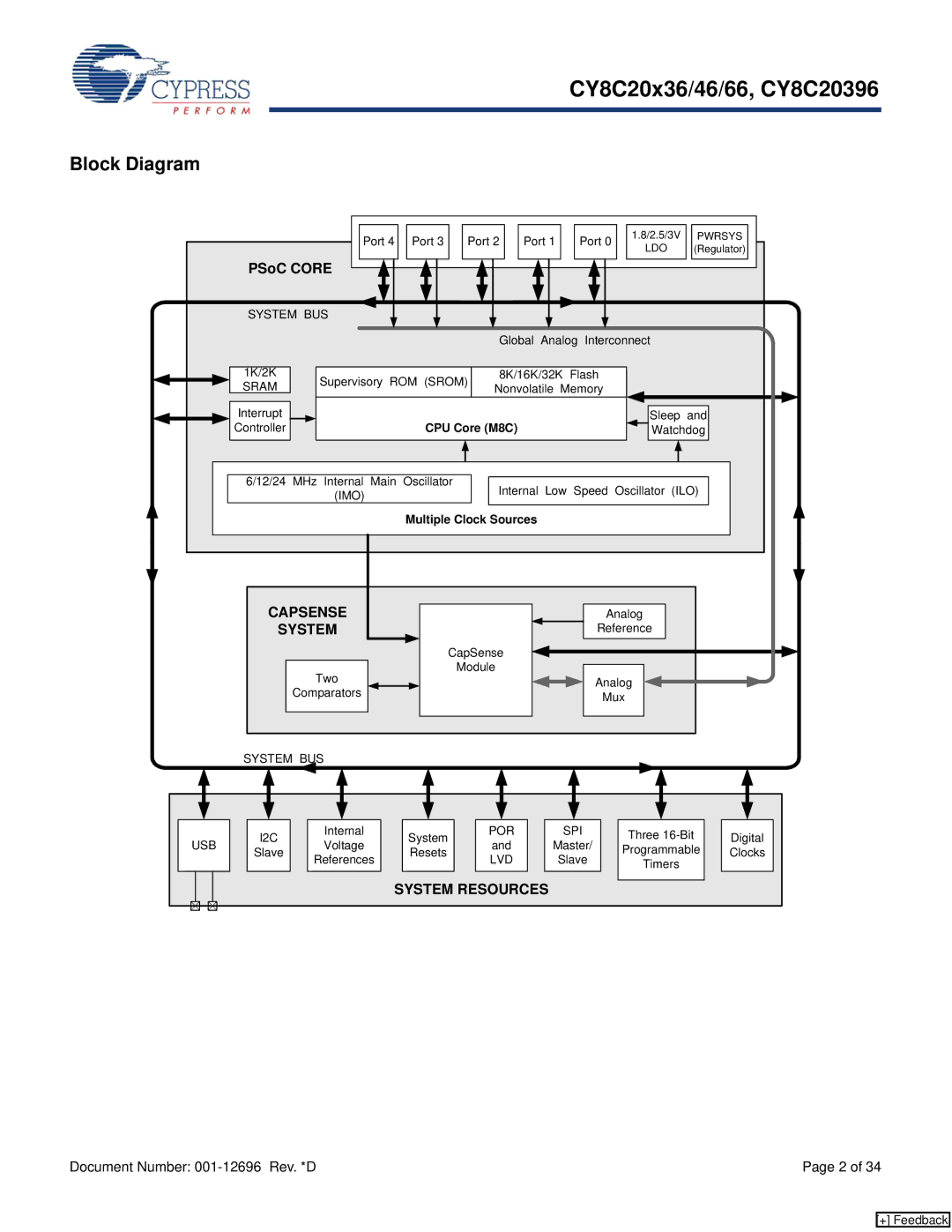

Block Diagram

| Port 4 | Port 3 |

| Port 2 | Port 1 |

| Port 0 | 1.8/2.5/3V | PWRSYS | ||||

|

|

| LDO |

| (Regulator) | ||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||

PSoC CORE |

|

|

|

|

|

|

|

|

|

|

|

| |

SYSTEM BUS |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| Global | Analog | Interconnect |

|

| |||

1K/2K | Supervisory ROM (SROM) | 8K/16K/32K Flash |

|

|

| ||||||||

SRAM | Nonvolatile Memory |

|

|

| |||||||||

|

|

|

|

|

|

|

| ||||||

Interrupt |

|

|

|

|

|

|

|

|

|

| Sleep | and | |

Controller |

|

| CPU Core (M8C) |

|

|

|

| Watchdog | |||||

6/12/24 | MHz Internal | Main Oscillator |

| Internal | Low | Speed | Oscillator | (ILO) | |||||

| (IMO) |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| Multiple Clock Sources |

|

|

|

|

|

| ||||

CAPSENSE |

|

|

|

|

|

|

|

| Analog |

|

| ||

SYSTEM |

|

|

|

|

|

|

|

| Reference |

|

| ||

|

|

|

| CapSense |

|

|

|

|

|

|

| ||

| Two |

|

|

| Module |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| Analog |

|

| ||

| Comparators |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| Mux |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| ||

SYSTEM BUS

| I2C | Internal | System | POR | SPI | Three | Digital | |

USB | Voltage | and | Master/ | |||||

Slave | Resets | Programmable | Clocks | |||||

| References | LVD | Slave | |||||

|

|

| Timers |

| ||||

|

|

|

|

|

|

| ||

|

|

| SYSTEM RESOURCES |

|

|

| ||

Document Number: | Page 2 of 34 |

[+] Feedback