CY8C20x36/46/66, CY8C20396

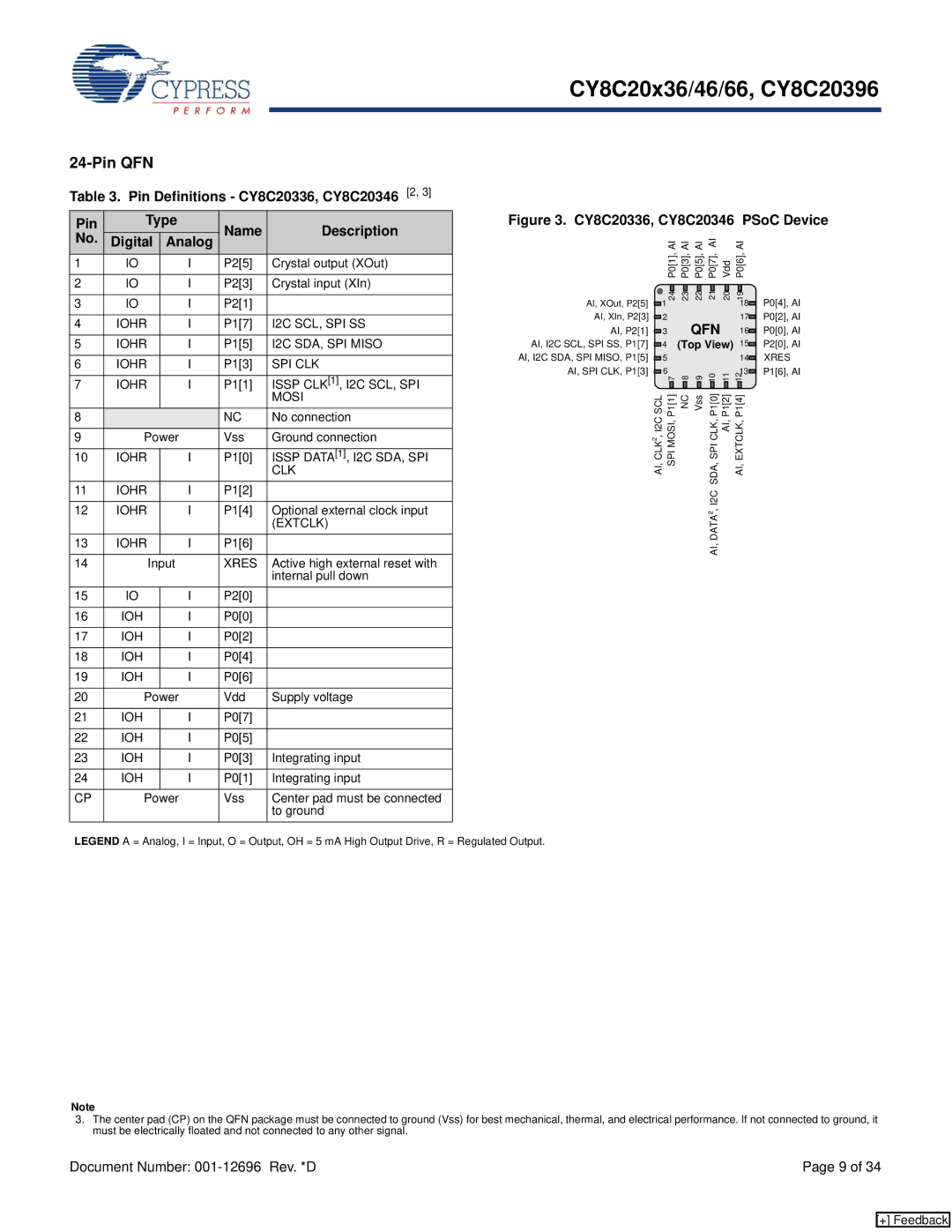

24-Pin QFN

Table 3. Pin Definitions - CY8C20336, CY8C20346 [2, 3]

Pin | Type | Name | Description | |

No. | Digital | Analog | ||

1 | IO | I | P2[5] | Crystal output (XOut) |

|

|

|

|

|

2 | IO | I | P2[3] | Crystal input (XIn) |

|

|

|

|

|

3 | IO | I | P2[1] |

|

|

|

|

|

|

4 | IOHR | I | P1[7] | I2C SCL, SPI SS |

|

|

|

|

|

5 | IOHR | I | P1[5] | I2C SDA, SPI MISO |

|

|

|

|

|

6 | IOHR | I | P1[3] | SPI CLK |

|

|

|

|

|

7 | IOHR | I | P1[1] | ISSP CLK[1], I2C SCL, SPI |

|

|

|

| MOSI |

8 |

|

| NC | No connection |

9 | Power | Vss | Ground connection | |

|

|

|

|

|

10 | IOHR | I | P1[0] | ISSP DATA[1], I2C SDA, SPI |

|

|

|

| CLK |

11 | IOHR | I | P1[2] |

|

|

|

|

|

|

12 | IOHR | I | P1[4] | Optional external clock input |

|

|

|

| (EXTCLK) |

13 | IOHR | I | P1[6] |

|

|

|

|

|

|

14 | Input | XRES | Active high external reset with | |

|

|

|

| internal pull down |

15 | IO | I | P2[0] |

|

|

|

|

|

|

16 | IOH | I | P0[0] |

|

|

|

|

|

|

17 | IOH | I | P0[2] |

|

|

|

|

|

|

18 | IOH | I | P0[4] |

|

|

|

|

|

|

19 | IOH | I | P0[6] |

|

|

|

|

|

|

20 | Power | Vdd | Supply voltage | |

|

|

|

|

|

21 | IOH | I | P0[7] |

|

|

|

|

|

|

22 | IOH | I | P0[5] |

|

|

|

|

|

|

23 | IOH | I | P0[3] | Integrating input |

|

|

|

|

|

24 | IOH | I | P0[1] | Integrating input |

|

|

|

|

|

CP | Power | Vss | Center pad must be connected | |

|

|

|

| to ground |

Figure 3. CY8C20336, CY8C20346 PSoC Device

|

| AI AI AI | AI |

|

| AI |

| |||||||||

|

| P0[1], | P0[3], | P0[5], | P0[7], | Vdd | P0[6], |

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AI, XOut, P2[5] |

|

| 24 | 23 | 22 | 21 |

| 20 | 19 |

| P0[4], AI | |||||

| 1 |

|

|

|

|

|

|

|

|

|

| 18 |

| |||

|

|

|

|

|

|

|

|

|

|

|

| |||||

AI, XIn, P2[3] |

| 2 |

|

|

| QFN |

|

| 17 |

| P0[2], AI | |||||

|

|

|

|

|

| |||||||||||

AI, P2[1] |

| 3 |

|

|

|

|

| 16 |

| P0[0], AI | ||||||

|

|

|

|

|

| |||||||||||

AI, I2C SCL, SPI SS, P1[7] |

| 4 |

| (Top View) 15 |

| P2[0], AI | ||||||||||

|

| |||||||||||||||

AI, I2C SDA, SPI MISO, P1[5] |

| 5 |

|

|

|

|

|

|

|

|

| 14 |

| XRES | ||

|

|

|

|

|

|

|

|

|

| |||||||

AI, SPI CLK, P1[3] |

| 6 |

|

|

|

|

| 10 |

|

|

| 13 |

| P1[6], AI | ||

|

|

| 7 | 8 | 9 |

| 11 12 |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

I2CSCL | P1[1] | NC | Vss | P1[0] | P1[2] | P1[4] |

| |||||||||

CLKAI, | SPIMOSI, |

|

|

|

| SPISDA,CLK, | AI, | EXTCLK,AI, |

| |||||||

, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| , I2C |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| AI, DATA |

|

|

|

|

|

| |

LEGEND A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

Note

3.The center pad (CP) on the QFN package must be connected to ground (Vss) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

Document Number: | Page 9 of 34 |

[+] Feedback