CY8C20x36/46/66, CY8C20396

AC External Clock Specifications

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 29. AC External Clock Specifications

Symbol | Description | Conditions | Min | Typ | Max | Units |

FOSCEXT | Frequency |

| 0.750 | – | 25.2 | MHz |

– | High Period |

| 20.6 | – | 5300 | ns |

|

|

|

|

|

|

|

– | Low Period |

| 20.6 | – | – | ns |

|

|

|

|

|

|

|

– | Power Up IMO to Switch |

| 150 | – | – | μs |

|

|

|

|

|

|

|

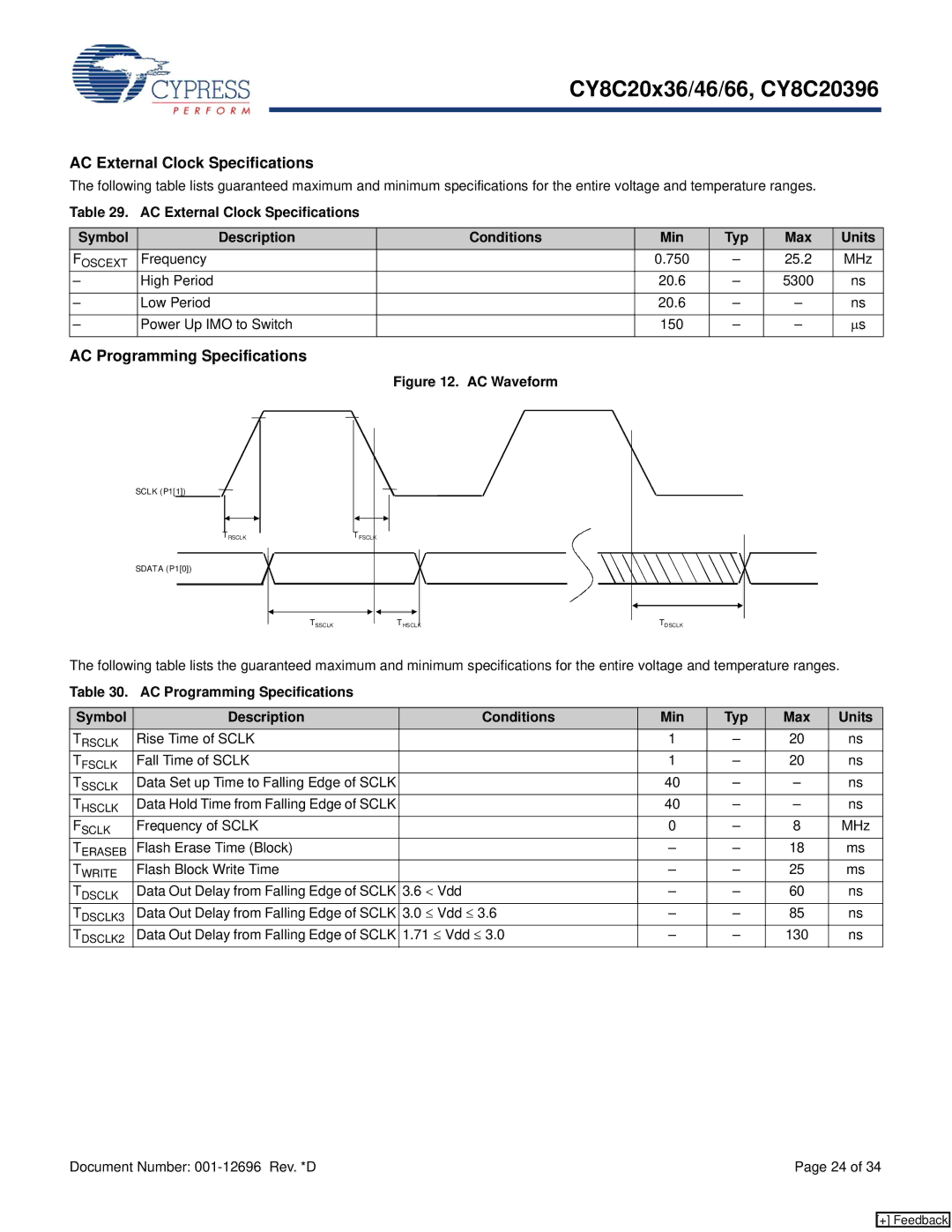

AC Programming Specifications

Figure 12. AC Waveform

SCLK (P1[1])

TRSCLK

SDATA (P1[0])

| TFSCLK |

TSSCLK | THSCLK |

TDSCLK |

The following table lists the guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 30. AC Programming Specifications

Symbol | Description |

| Conditions | Min | Typ | Max | Units |

TRSCLK | Rise Time of SCLK |

|

| 1 | – | 20 | ns |

TFSCLK | Fall Time of SCLK |

|

| 1 | – | 20 | ns |

TSSCLK | Data Set up Time to Falling Edge of SCLK |

|

| 40 | – | – | ns |

THSCLK | Data Hold Time from Falling Edge of SCLK |

|

| 40 | – | – | ns |

FSCLK | Frequency of SCLK |

|

| 0 | – | 8 | MHz |

TERASEB | Flash Erase Time (Block) |

|

| – | – | 18 | ms |

TWRITE | Flash Block Write Time |

|

| – | – | 25 | ms |

TDSCLK | Data Out Delay from Falling Edge of SCLK | 3.6 < Vdd |

| – | – | 60 | ns |

TDSCLK3 | Data Out Delay from Falling Edge of SCLK | 3.0 ≤ Vdd ≤ 3.6 | – | – | 85 | ns | |

TDSCLK2 | Data Out Delay from Falling Edge of SCLK | 1.71 ≤ Vdd ≤ 3.0 | – | – | 130 | ns | |

Document Number: | Page 24 of 34 |

[+] Feedback