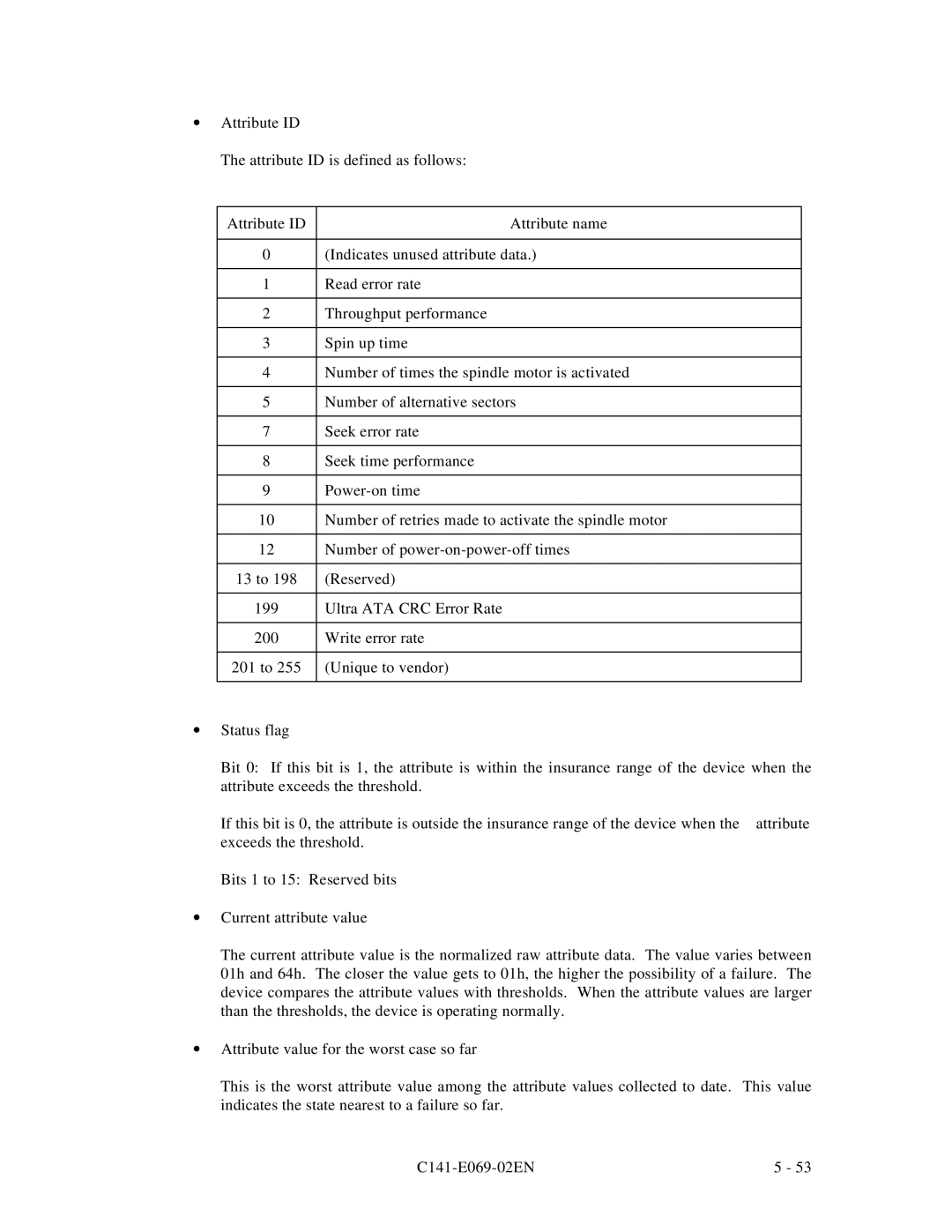

∙Attribute ID

The attribute ID is defined as follows:

Attribute ID | Attribute name |

|

|

0 | (Indicates unused attribute data.) |

|

|

1 | Read error rate |

|

|

2 | Throughput performance |

|

|

3 | Spin up time |

|

|

4 | Number of times the spindle motor is activated |

|

|

5 | Number of alternative sectors |

|

|

7 | Seek error rate |

|

|

8 | Seek time performance |

|

|

9 | |

|

|

10 | Number of retries made to activate the spindle motor |

|

|

12 | Number of |

|

|

13 to 198 | (Reserved) |

|

|

199 | Ultra ATA CRC Error Rate |

|

|

200 | Write error rate |

|

|

201 to 255 | (Unique to vendor) |

|

|

∙Status flag

Bit 0: If this bit is 1, the attribute is within the insurance range of the device when the attribute exceeds the threshold.

If this bit is 0, the attribute is outside the insurance range of the device when the attribute exceeds the threshold.

Bits 1 to 15: Reserved bits

∙Current attribute value

The current attribute value is the normalized raw attribute data. The value varies between 01h and 64h. The closer the value gets to 01h, the higher the possibility of a failure. The device compares the attribute values with thresholds. When the attribute values are larger than the thresholds, the device is operating normally.

∙Attribute value for the worst case so far

This is the worst attribute value among the attribute values collected to date. This value indicates the state nearest to a failure so far.

| 5 - 53 |