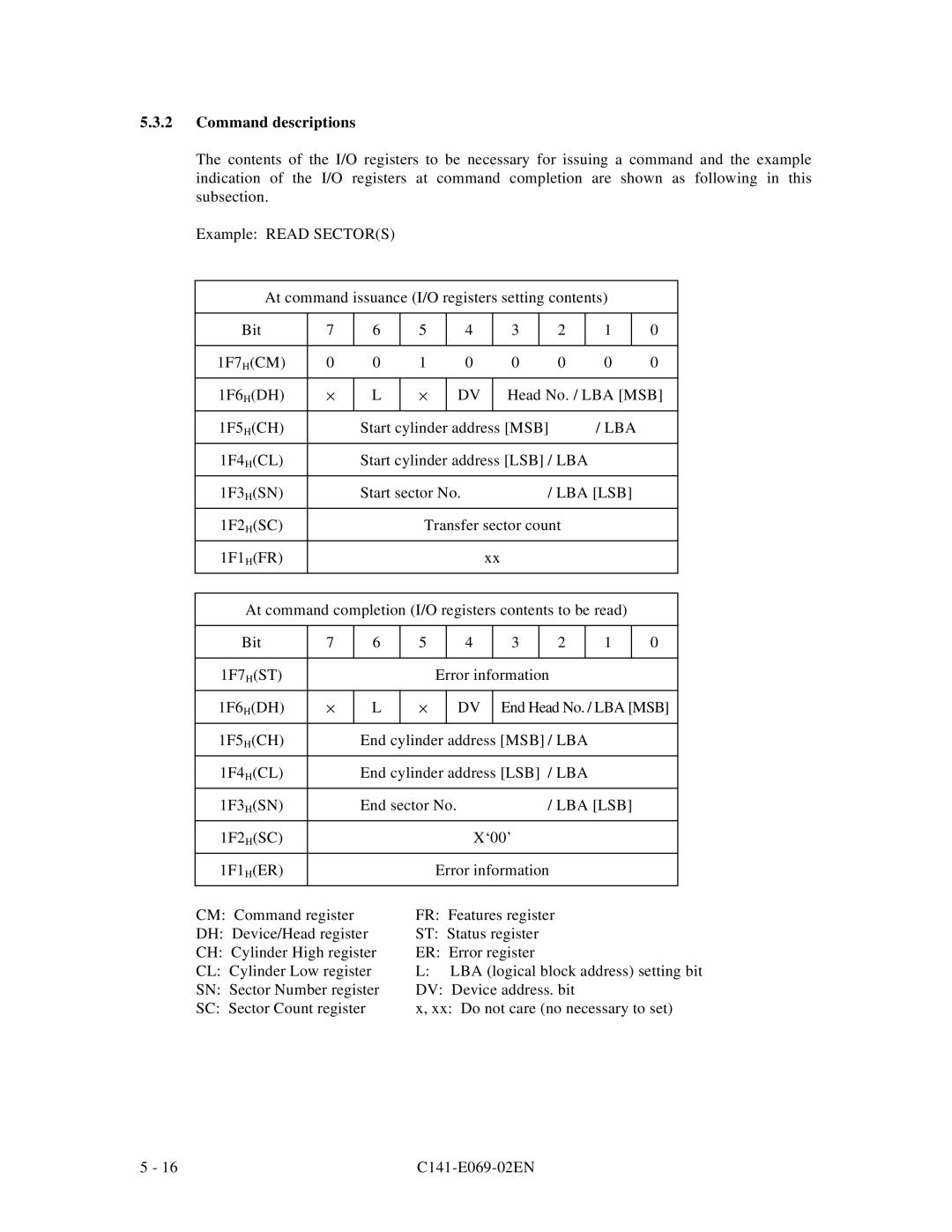

5.3.2Command descriptions

The contents of the I/O registers to be necessary for issuing a command and the example indication of the I/O registers at command completion are shown as following in this subsection.

Example: READ SECTOR(S)

At command issuance (I/O registers setting contents)

Bit | 7 | 6 | 5 | 4 |

| 3 | 2 |

| 1 |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

1F7H(CM) | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 |

| 0 | |

|

|

|

|

|

|

| |||||

1F6H(DH) | × | L | × | DV |

| Head No. / LBA [MSB] | |||||

|

|

|

|

|

|

|

| ||||

1F5H(CH) |

| Start cylinder address [MSB] | / LBA |

| |||||||

|

|

|

|

|

| ||||||

1F4H(CL) |

| Start cylinder address [LSB] / LBA |

|

|

| ||||||

|

|

|

|

|

|

| |||||

1F3H(SN) |

| Start sector No. |

|

| / LBA [LSB] |

| |||||

|

|

|

|

|

|

| |||||

1F2H(SC) |

|

| Transfer sector count |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| |

1F1H(FR) |

|

|

|

| xx |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

At command completion (I/O registers contents to be read)

Bit | 7 | 6 | 5 |

| 4 | 3 |

| 2 |

| 1 |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

| |

1F7H(ST) |

|

| Error information |

|

|

|

|

| ||||

|

|

|

|

|

|

| ||||||

1F6H(DH) | × | L | × |

| DV | End Head No. / LBA [MSB] | ||||||

|

|

|

|

|

|

|

|

| ||||

1F5H(CH) |

| End cylinder address [MSB] / LBA |

|

|

| |||||||

|

|

|

|

|

| |||||||

1F4H(CL) |

| End cylinder address [LSB] / LBA |

|

|

| |||||||

|

|

|

|

|

|

| ||||||

1F3H(SN) |

| End sector No. |

|

| / LBA [LSB] |

| ||||||

|

|

|

|

|

|

|

|

|

|

| ||

1F2H(SC) |

|

|

|

| X‘00’ |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||||

1F1H(ER) |

|

| Error information |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

CM: | Command register | FR: Features register |

DH: | Device/Head register | ST: Status register |

CH: | Cylinder High register | ER: Error register |

CL: | Cylinder Low register | L: LBA (logical block address) setting bit |

SN: | Sector Number register | DV: Device address. bit |

SC: | Sector Count register | x, xx: Do not care (no necessary to set) |

5 - 16 |

|