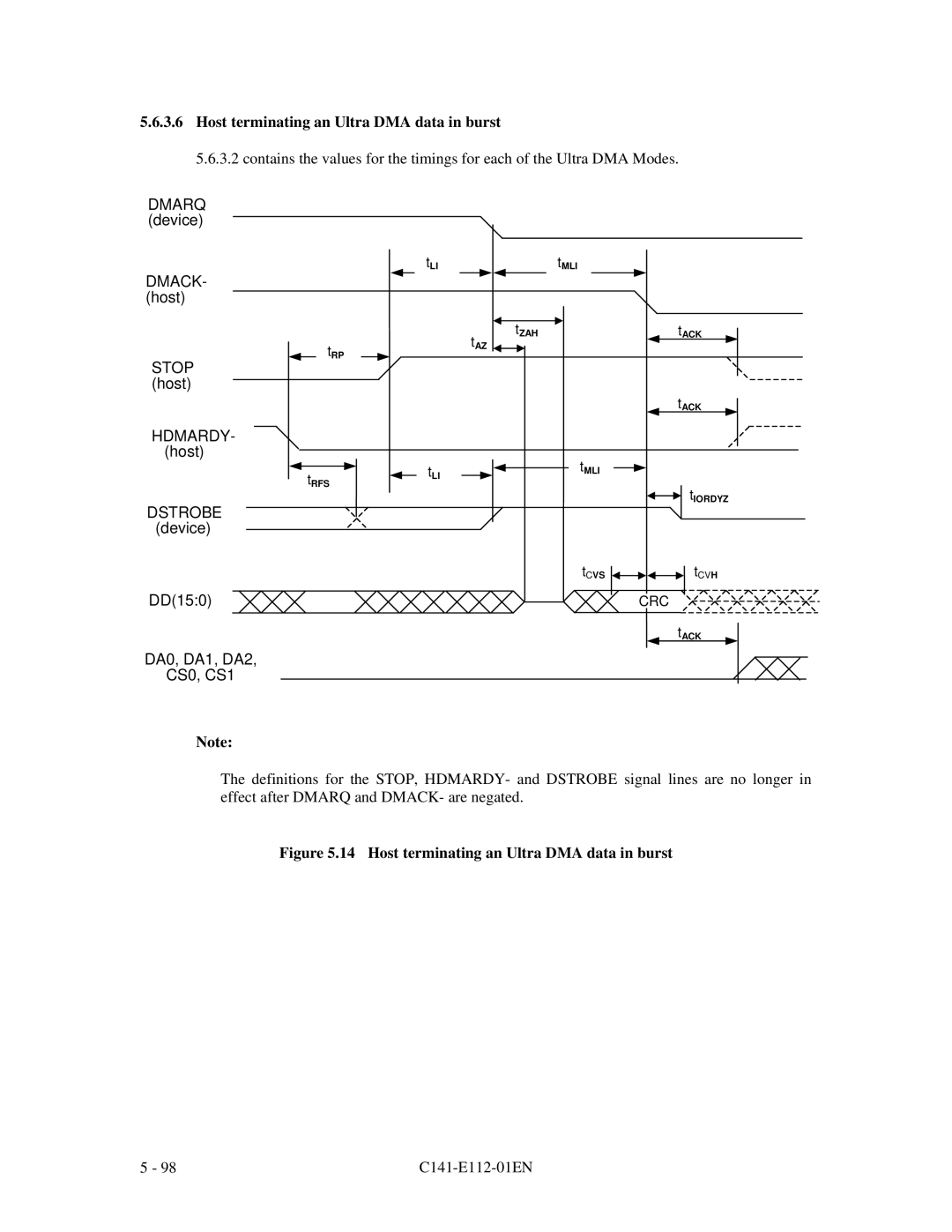

5.6.3.6Host terminating an Ultra DMA data in burst

5.6.3.2 contains the values for the timings for each of the Ultra DMA Modes.

DMARQ (device)

|

|

|

|

|

| tLI |

|

|

|

|

|

| tMLI |

|

|

|

| ||

DMACK- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

(host) |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tZAH |

|

|

|

|

|

| tACK |

|

|

|

|

|

|

|

| tAZ |

|

|

|

|

|

| ||||||

|

| tRP |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

STOP |

|

|

|

|

|

|

|

|

| ||||||||||

(host) |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tACK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HDMARDY- (host)

tRFS![]() tLI

tLI ![]()

![]() tMLI

tMLI

DSTROBE (device)

tCVS

DD(15:0)

tIORDYZ

tCVH

CRC

tACK

DA0, DA1, DA2,

CS0, CS1

Note:

The definitions for the STOP, HDMARDY- and DSTROBE signal lines are no longer in effect after DMARQ and DMACK- are negated.

Figure 5.14 Host terminating an Ultra DMA data in burst

5 - 98 |

|