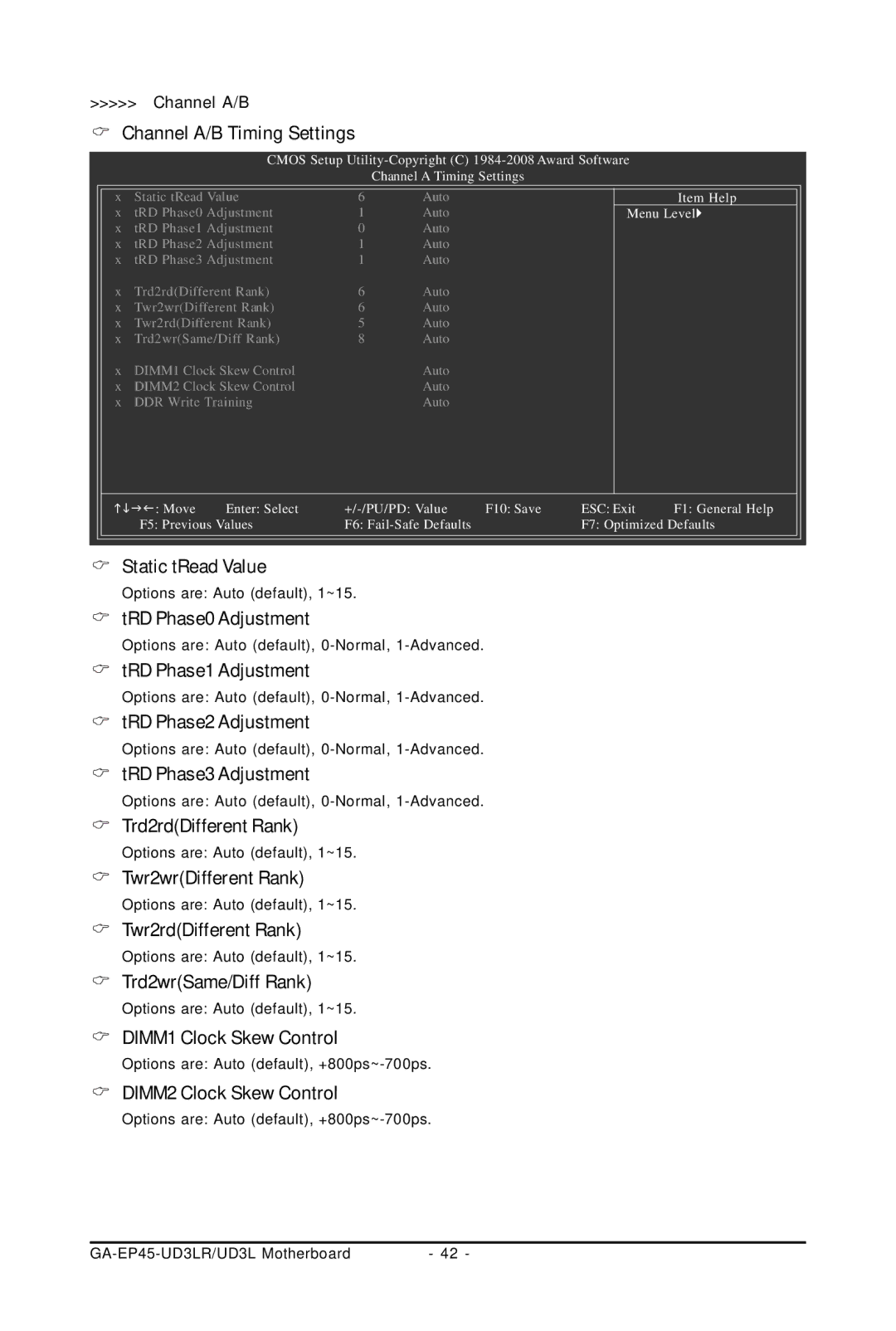

>>>>> Channel A/B

Channel A/B Timing Settings

CMOS Setup

Channel A Timing Settings

x | Static tRead Value | 6 | Auto |

|

| Item Help | |

x | tRD Phase0 Adjustment | 1 | Auto |

| Menu Level | ||

x | tRD Phase1 Adjustment | 0 | Auto |

|

|

| |

x | tRD Phase2 Adjustment | 1 | Auto |

|

|

| |

x | tRD Phase3 Adjustment | 1 | Auto |

|

|

| |

x | Trd2rd(Different Rank) | 6 | Auto |

|

|

| |

x | Twr2wr(Different Rank) | 6 | Auto |

|

|

| |

x | Twr2rd(Different Rank) | 5 | Auto |

|

|

| |

x | Trd2wr(Same/Diff Rank) | 8 | Auto |

|

|

| |

x DIMM1 Clock Skew Control |

| Auto |

|

|

| ||

x DIMM2 Clock Skew Control |

| Auto |

|

|

| ||

x | DDR Write Training |

| Auto |

|

|

| |

: Move | Enter: Select | F10: Save | ESC: Exit | F1: General Help | |||

| F5: Previous Values | F6: |

| F7: Optimized Defaults | |||

Static tRead Value

Options are: Auto (default), 1~15.

tRD Phase0 Adjustment

Options are: Auto (default),

tRD Phase1 Adjustment

Options are: Auto (default),

tRD Phase2 Adjustment

Options are: Auto (default),

tRD Phase3 Adjustment

Options are: Auto (default),

Trd2rd(Different Rank)

Options are: Auto (default), 1~15.

Twr2wr(Different Rank)

Options are: Auto (default), 1~15.

Twr2rd(Different Rank)

Options are: Auto (default), 1~15.

Trd2wr(Same/Diff Rank)

Options are: Auto (default), 1~15.

DIMM1 Clock Skew Control

Options are: Auto (default),

DIMM2 Clock Skew Control

Options are: Auto (default),

- 42 - |