Networking Silicon — 82540EP

4.5.1.2PCI Bus Interface Timing

Table 15. PCI Bus Interface Timing Parameters

Symbol | Parameter | PCI 66MHz | PCI 33 MHz | Units | |||

|

|

|

| ||||

|

| Min | Max | Min | Max |

| |

|

|

|

|

|

|

| |

TVAL | CLK to signal valid delay: bussed | 2 | 6 | 2 | 11 | ns | |

signals | |||||||

|

|

|

|

|

| ||

|

|

|

|

|

|

| |

TVAL(ptp) | CLK to signal valid delay: point- | 2 | 6 | 2 | 12 | ns | |

|

|

|

|

|

| ||

|

|

|

|

|

|

| |

TON | Float to active delay | 2 |

| 2 |

| ns | |

|

|

|

|

|

|

| |

TOFF | Active to float delay |

| 14 |

| 28 | ns | |

|

|

|

|

|

|

| |

TSU | Input setup time to CLK: bussed | 3 |

| 7 |

| ns | |

signals |

|

| |||||

|

|

|

|

|

| ||

|

|

|

|

|

|

| |

TSU(ptp) | Input setup time to CLK: | 5 |

| 10, 12 |

| ns | |

point signals |

|

| |||||

|

|

|

|

|

| ||

|

|

|

|

|

|

| |

TH | Input hold time from CLK | 0 |

| 0 |

| ns | |

|

|

|

|

|

|

| |

TRRSU | REQ64# to RST# setup time | 10*TCYC |

| 10*TCYC |

| ns | |

|

|

|

|

|

|

| |

TRRH | RST# to REQ64# hold time | 0 |

| 0 |

| ns | |

|

|

|

|

|

|

| |

NOTES:

1.Output timing measurements are as shown.

2.REQ# and GNT# signals are

3.Input timing measurements are as shown.

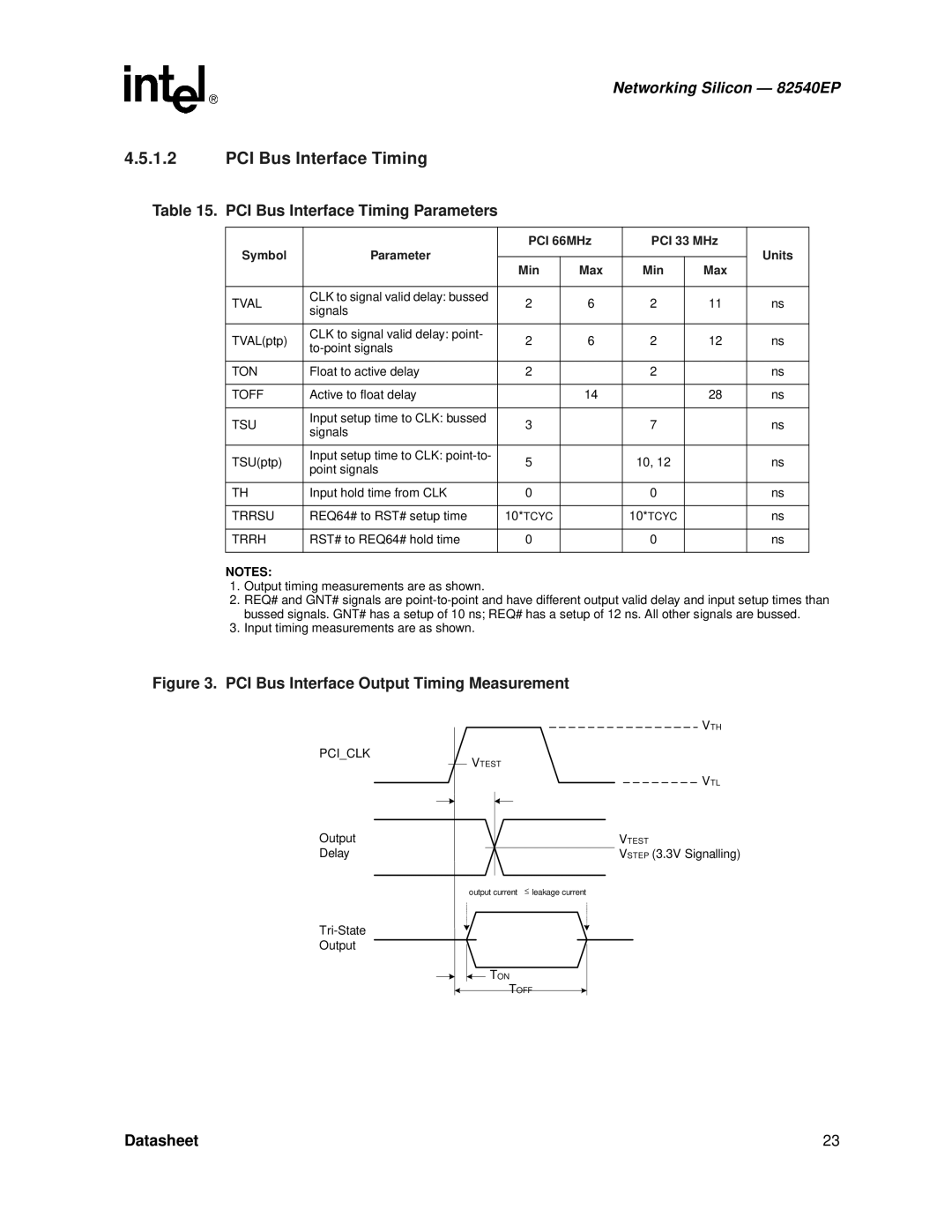

Figure 3. PCI Bus Interface Output Timing Measurement

PCI_CLK

Output

Delay

VTH

VTEST

VTL

VTEST

VSTEP (3.3V Signalling)

output current ≤ leakage current

TON

TOFF

Datasheet | 23 |