Introduction

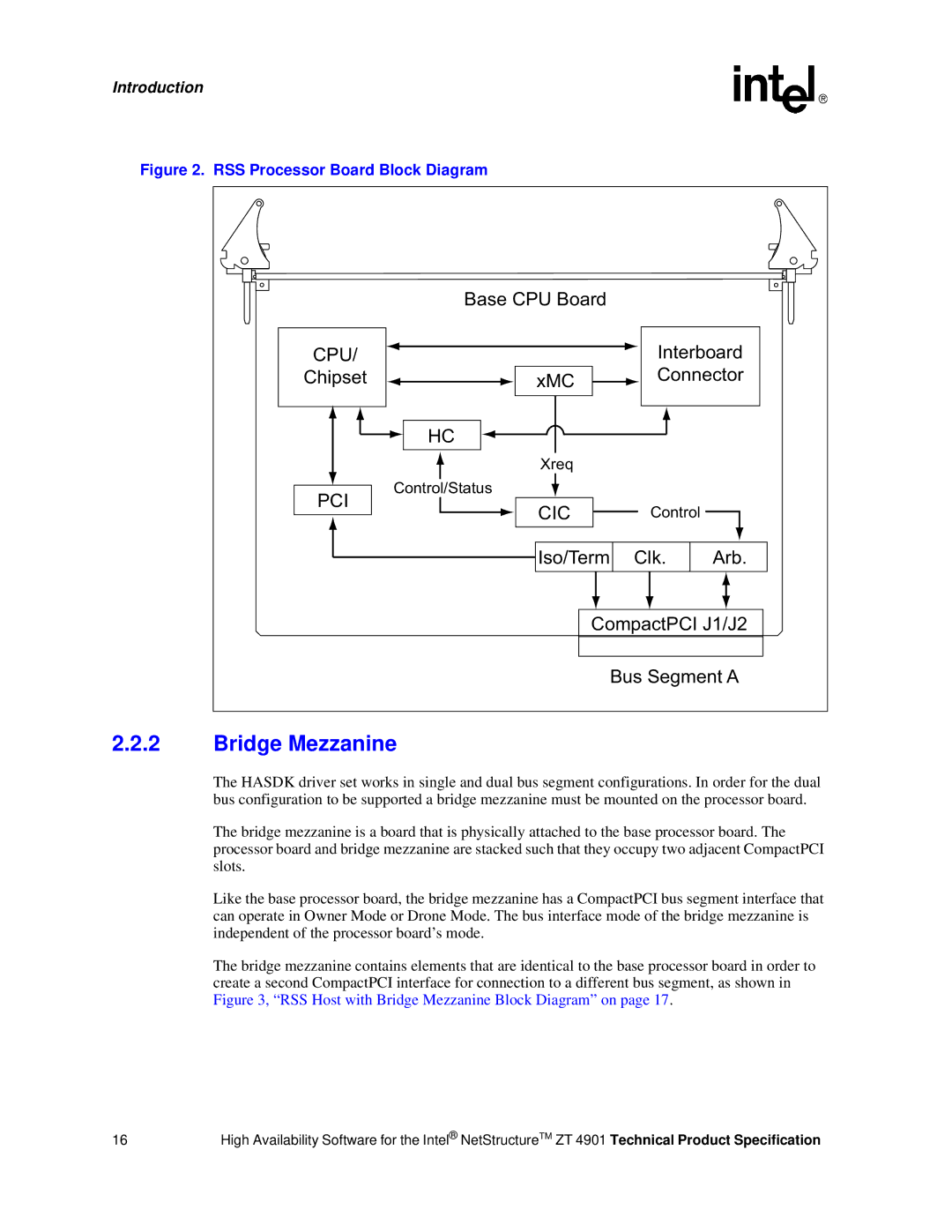

Figure 2. RSS Processor Board Block Diagram

| Base CPU Board |

|

|

CPU/ |

| Interboard | |

Chipset | xMC | Connector | |

| HC |

|

|

| Xreq |

|

|

PCI | Control/Status |

|

|

CIC | Control |

| |

|

| ||

| Iso/Term | Clk. | Arb. |

| CompactPCI J1/J2 | ||

|

| Bus Segment A | |

2.2.2Bridge Mezzanine

The HASDK driver set works in single and dual bus segment configurations. In order for the dual bus configuration to be supported a bridge mezzanine must be mounted on the processor board.

The bridge mezzanine is a board that is physically attached to the base processor board. The processor board and bridge mezzanine are stacked such that they occupy two adjacent CompactPCI slots.

Like the base processor board, the bridge mezzanine has a CompactPCI bus segment interface that can operate in Owner Mode or Drone Mode. The bus interface mode of the bridge mezzanine is independent of the processor board’s mode.

The bridge mezzanine contains elements that are identical to the base processor board in order to create a second CompactPCI interface for connection to a different bus segment, as shown in Figure 3, “RSS Host with Bridge Mezzanine Block Diagram” on page 17.

16 | High Availability Software for the Intel® NetStructureTM ZT 4901 Technical Product Specification |