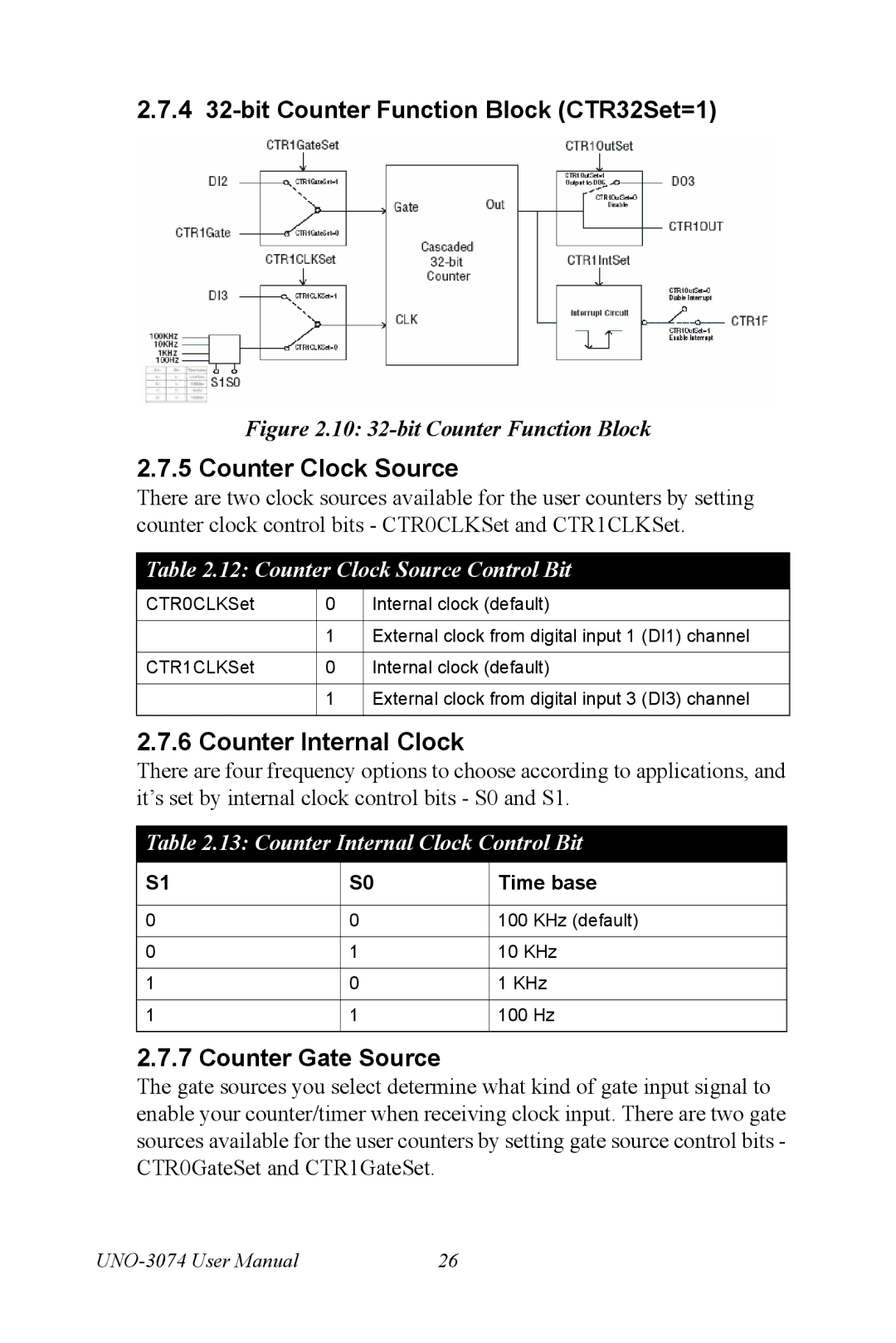

2.7.4 32-bit Counter Function Block (CTR32Set=1)

Figure 2.10: 32-bit Counter Function Block

2.7.5 Counter Clock Source

There are two clock sources available for the user counters by setting counter clock control bits - CTR0CLKSet and CTR1CLKSet.

Table 2.12: Counter Clock Source Control Bit

CTR0CLKSet | 0 | Internal clock (default) |

|

|

|

| 1 | External clock from digital input 1 (DI1) channel |

|

|

|

CTR1CLKSet | 0 | Internal clock (default) |

1External clock from digital input 3 (DI3) channel

2.7.6Counter Internal Clock

There are four frequency options to choose according to applications, and it’s set by internal clock control bits - S0 and S1.

Table 2.13: Counter Internal Clock Control Bit

S1 | S0 | Time base |

|

|

|

0 | 0 | 100 KHz (default) |

|

|

|

0 | 1 | 10 KHz |

|

|

|

1 | 0 | 1 KHz |

|

|

|

1 | 1 | 100 Hz |

|

|

|

2.7.7 Counter Gate Source

The gate sources you select determine what kind of gate input signal to enable your counter/timer when receiving clock input. There are two gate sources available for the user counters by setting gate source control bits - CTR0GateSet and CTR1GateSet.

26 |