2.7 Onboard Isolated Counter/Timer

The

The

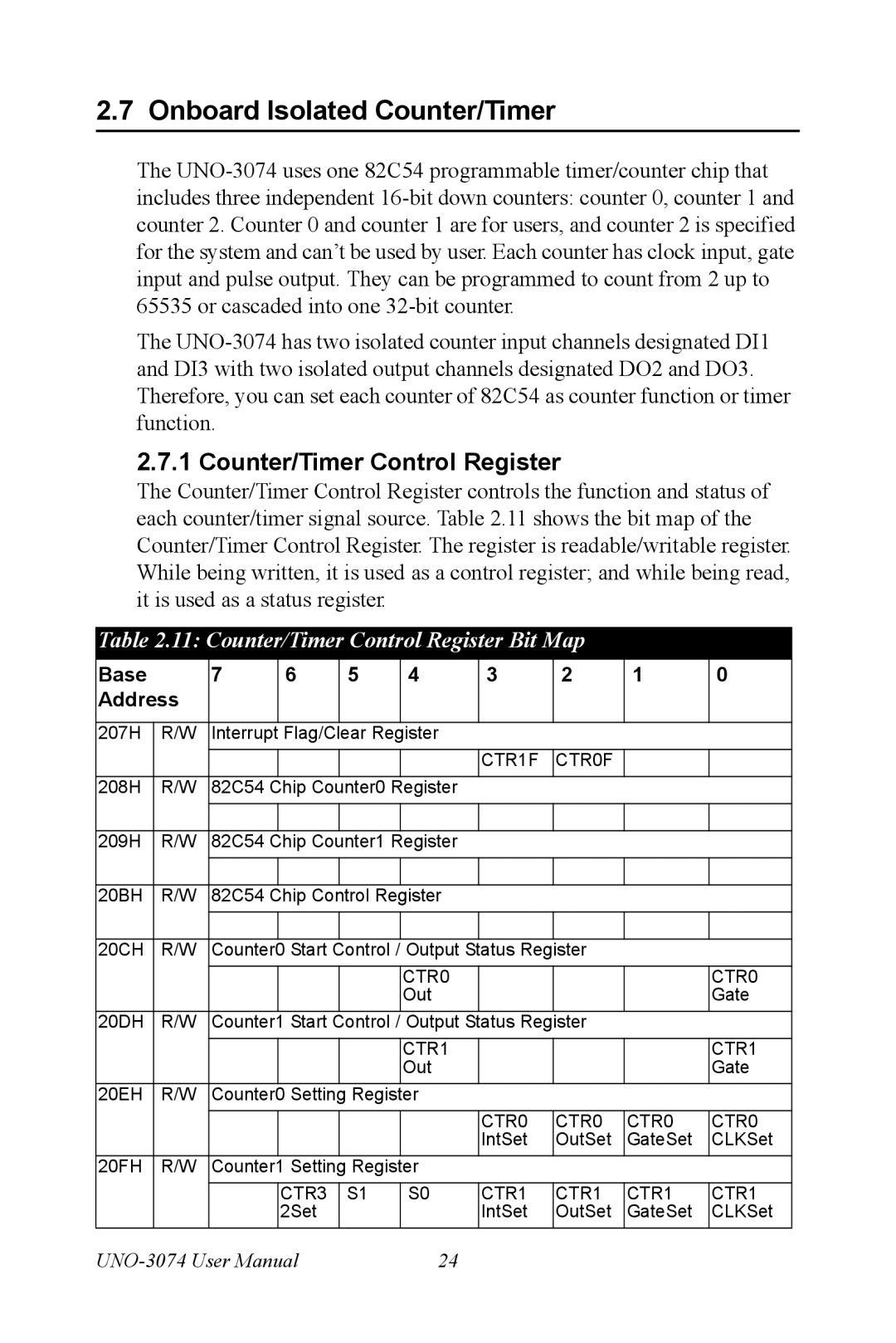

2.7.1 Counter/Timer Control Register

The Counter/Timer Control Register controls the function and status of each counter/timer signal source. Table 2.11 shows the bit map of the Counter/Timer Control Register. The register is readable/writable register. While being written, it is used as a control register; and while being read, it is used as a status register.

Table 2.11: Counter/Timer Control Register Bit Map

Base |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Address |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

207H | R/W | Interrupt | Flag/Clear Register |

|

|

|

| ||

|

|

|

|

|

| CTR1F | CTR0F |

|

|

208H | R/W | 82C54 | Chip Counter0 Register |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

209H | R/W | 82C54 | Chip Counter1 Register |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

20BH | R/W | 82C54 | Chip Control Register |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

20CH | R/W | Counter0 | Start | Control / | Output Status Register |

|

| ||

|

|

|

|

| CTR0 |

|

|

| CTR0 |

|

|

|

|

| Out |

|

|

| Gate |

20DH | R/W | Counter1 | Start | Control / | Output Status Register |

|

| ||

|

|

|

|

| CTR1 |

|

|

| CTR1 |

|

|

|

|

| Out |

|

|

| Gate |

20EH | R/W | Counter0 | Setting | Register |

|

|

|

| |

|

|

|

|

|

| CTR0 | CTR0 | CTR0 | CTR0 |

|

|

|

|

|

| IntSet | OutSet | GateSet | CLKSet |

20FH | R/W | Counter1 | Setting | Register |

|

|

|

| |

|

|

| CTR3 | S1 | S0 | CTR1 | CTR1 | CTR1 | CTR1 |

|

|

| 2Set |

|

| IntSet | OutSet | GateSet | CLKSet |

24 |