Chapter 4 Functional Description

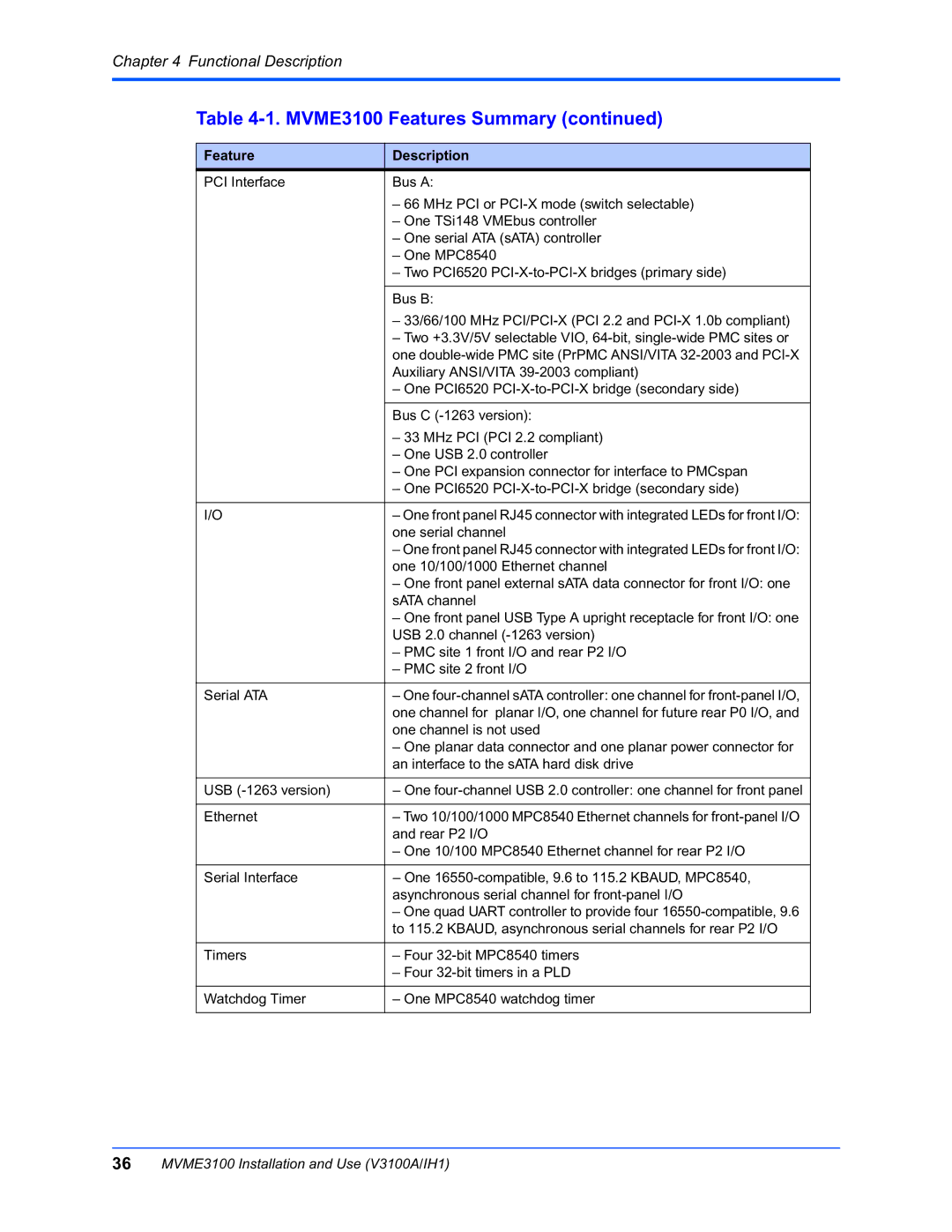

Table 4-1. MVME3100 Features Summary (continued)

Feature | Description |

PCI Interface | Bus A: |

| – 66 MHz PCI or |

| – One TSi148 VMEbus controller |

| – One serial ATA (sATA) controller |

| – One MPC8540 |

| – Two PCI6520 |

|

|

| Bus B: |

| – 33/66/100 MHz |

| – Two +3.3V/5V selectable VIO, |

| one |

| Auxiliary ANSI/VITA |

| – One PCI6520 |

|

|

| Bus C |

| – 33 MHz PCI (PCI 2.2 compliant) |

| – One USB 2.0 controller |

| – One PCI expansion connector for interface to PMCspan |

| – One PCI6520 |

|

|

I/O | – One front panel RJ45 connector with integrated LEDs for front I/O: |

| one serial channel |

| – One front panel RJ45 connector with integrated LEDs for front I/O: |

| one 10/100/1000 Ethernet channel |

| – One front panel external sATA data connector for front I/O: one |

| sATA channel |

| – One front panel USB Type A upright receptacle for front I/O: one |

| USB 2.0 channel |

| – PMC site 1 front I/O and rear P2 I/O |

| – PMC site 2 front I/O |

|

|

Serial ATA | – One |

| one channel for planar I/O, one channel for future rear P0 I/O, and |

| one channel is not used |

| – One planar data connector and one planar power connector for |

| an interface to the sATA hard disk drive |

|

|

USB | – One |

|

|

Ethernet | – Two 10/100/1000 MPC8540 Ethernet channels for |

| and rear P2 I/O |

| – One 10/100 MPC8540 Ethernet channel for rear P2 I/O |

|

|

Serial Interface | – One |

| asynchronous serial channel for |

| – One quad UART controller to provide four |

| to 115.2 KBAUD, asynchronous serial channels for rear P2 I/O |

|

|

Timers | – Four |

| – Four |

|

|

Watchdog Timer | – One MPC8540 watchdog timer |

|

|

36MVME3100 Installation and Use (V3100A/IH1)