PM5358 | |

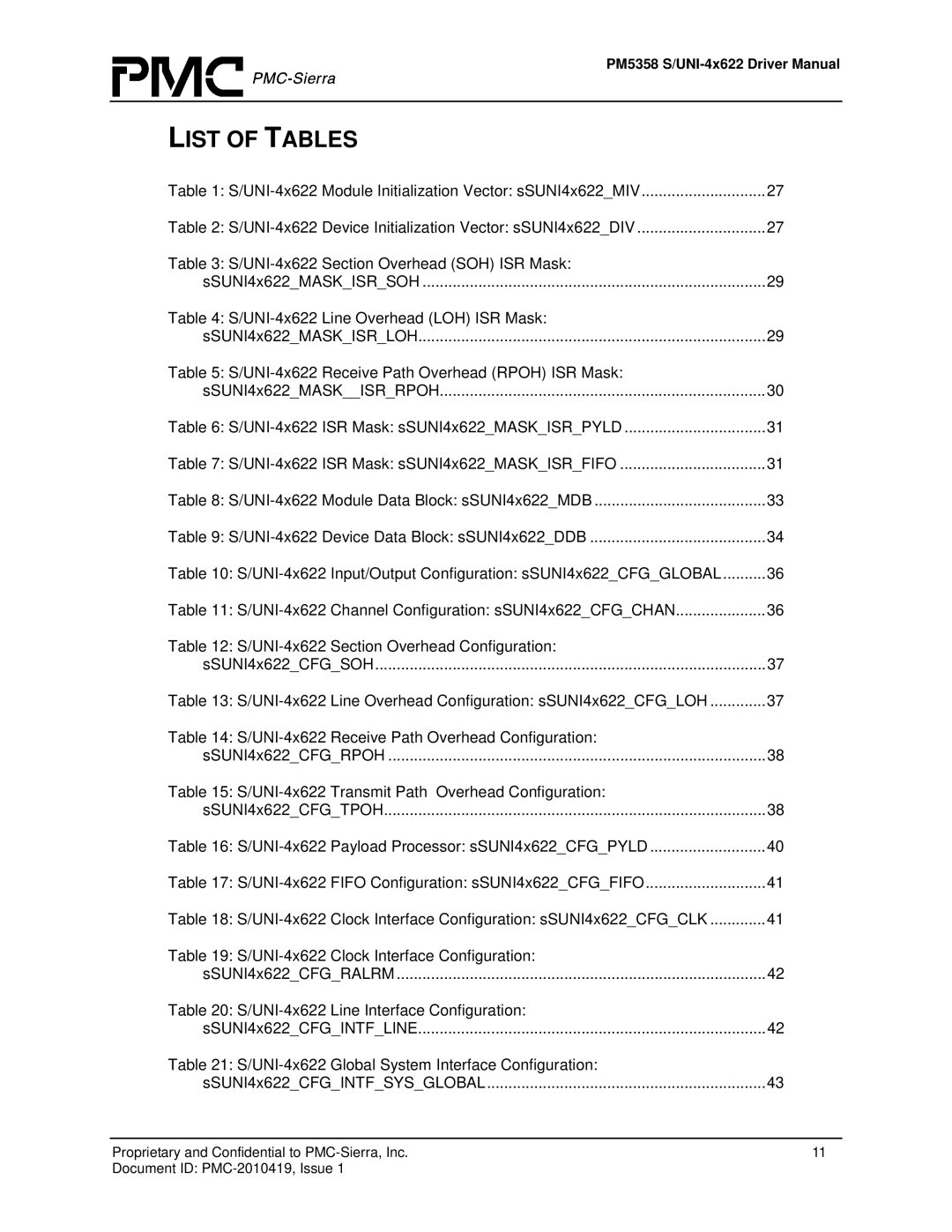

LIST OF TABLES |

|

Table 1: | 27 |

Table 2: | 27 |

Table 3: |

|

sSUNI4x622_MASK_ISR_SOH | 29 |

Table 4: |

|

sSUNI4x622_MASK_ISR_LOH | 29 |

Table 5: |

|

sSUNI4x622_MASK__ISR_RPOH | 30 |

Table 6: | 31 |

Table 7: | 31 |

Table 8: | 33 |

Table 9: | 34 |

Table 10: | 36 |

Table 11: | 36 |

Table 12: |

|

sSUNI4x622_CFG_SOH | 37 |

Table 13: | 37 |

Table 14: |

|

sSUNI4x622_CFG_RPOH | 38 |

Table 15: |

|

sSUNI4x622_CFG_TPOH | 38 |

Table 16: | 40 |

Table 17: | 41 |

Table 18: | 41 |

Table 19: |

|

sSUNI4x622_CFG_RALRM | 42 |

Table 20: |

|

sSUNI4x622_CFG_INTF_LINE | 42 |

Table 21: |

|

sSUNI4x622_CFG_INTF_SYS_GLOBAL | 43 |

Proprietary and Confidential to | 11 |

Document ID: |

|