Sun StorEdge 5310 NAS Troubleshooting Guide

Please Recycle

Contents

NAS Head 1 Hardware

Contents

Storage Arrays 1 Fibre Channel FC

Clustering 1 Overview Checkpoints/Snapshots 1 Overview

Viii Sun StorEdge 5310 NAS Troubleshooting Guide December

Tables

Boot Block Post Progress LED Code Table Port 80h Codes

Storage Array Status Icon Quick Reference Standard Terms

Figures

Array Management Window

Write ordering on the Mirror

Removing the SFP Transceiver and fibre Optic Cable

Preface

Table P-1Typographic Conventions

Who Should Use This Book

How This Manual is Organized

Typographic Conventions

Related Documentation

Accessing Sun Documentation Online

Ordering Sun Documents

Sun Welcomes Your Comments

Shell Prompts in Command Examples

Table P-2Shell Prompt

How to Use This Manual

Troubleshooting Overview

2Sun StorEdge 5310 NAS Troubleshooting Guide December

Troubleshooting Tools

High-Level Troubleshooting Tasks

Troubleshooting Procedures

Log Message Severity Levels

Initial Troubleshooting Guidelines

Troubleshooting Flow Charts

Follow the steps below to diagnose hardware problems

StorEdge Diagnostic Email

Diagnostic Information Sources

To collect diagnostics, proceed as follows

Collect general data

Accurately quantify the problem

Data Collection for Escalations

Collecting Information from the Sun StorEdge 5310 NAS

Data Collection for Specific Issues

Check remote access capabilities

Software compatibility issues

Security Issues

Cacls

User access token

Proc filesystem

StorEdge network capture utility

Network trace

Duplication instructions

Client and Server data

1List of Adapters

2.9 TCP/IP Connectivity problems

2Routing Table

Network Configuration

Performance Issues

Configuration

Other processes / High CPU Utilization

Command Line performance utilities

Understanding Sun StorEdge 5310 NAS Log Messages

Log Error Messages Syslog

Components of an Event Message

Time/date Severity

Severity Level Definitions highest to lowest

Sun StorEdge 5310 NAS Error Messages

About SysMon Error Notification

Table A-3UPS Error Messages

UPS Subsystem Errors

Controller Cache Disabled

Pems Events

File System Errors

Table A-4File System Errors

Table A-5PEMS Error Messages

Power supply failure

Electrostatic Discharge Information

Maintenance Precautions

Preparation Procedures

Tools Required

Grounding Procedure

Static Electricity Precautions

Static Electricity

28Sun StorEdge 5310 NAS Troubleshooting Guide December

Hardware Contacting Technical Support

NAS Head

Checklist

Problems With Initial System Startup

Shutdown Commands for Software Menu

Resetting the Server

Shutdown Commands for Hardware LCD Display

Specific Problems and Corrective Actions

Preparing the System for Diagnostic Testing

1Index to Problems

Server Does Not Power On

Problems Starting Up

Front Panel is Unresponsive and Video is Disabled

2Bootup Beep Codes

Server Beeps at Power On or When Booting

Power-On Self-Test Post

Server Starts Booting Automatically at Power On

System Cooling Fans Do Not Rotate Properly

Power LED Does Not Light

Verifying Proper Operation of Key System LEDs

Cannot Connect to a Server

Problems with Network

Diagnosing System Errors

Troubleshooting the Server Using Built- In Tools

Other Problems

Post Screen Messages

LEDs and Pushbuttons

LEDs

Beep Codes

Post

Front Panel LEDs and Pushbuttons

4Front Panel LEDs

Front Panel LEDs

14Sun StorEdge 5310 NAS Troubleshooting Guide December

5Front Panel Pushbuttons

Front Panel Pushbuttons

2Rear Panel LEDs 6Rear Panel LEDs

Rear Panel LEDs

6Rear Panel LEDs

Critical Condition

Front-Panel System Status LED

7System Status LED States

Degraded Condition

Non-Critical Condition

8Power Supply Status LED States

Rear Panel Power Supply Status LED

5Fault and Status LEDs on the Server Board

Server Main Board Fault LEDs

22Sun StorEdge 5310 NAS Troubleshooting Guide December

6Location of Front-Panel ID Pushbutton and LED

System ID LEDs

9Standard Post Error Messages and Codes

Power-On Self Test Post

System memory size error Yes

10Extended Post Error Messages and Codes

11BMC-Generated Post Beep Codes

Post Error Beep Codes

12BIOS-Generated Boot Block Post Beep Codes

0Ch

Bios Recovery Beep Codes

13Memory 3-Beep and LED Post Error Codes

08h

14BIOS Recovery Beep Codes

Post Progress Code LED Indicators

7Examples of Post LED Coding

15Boot Block Post Progress LED Code Table Port 80h Codes

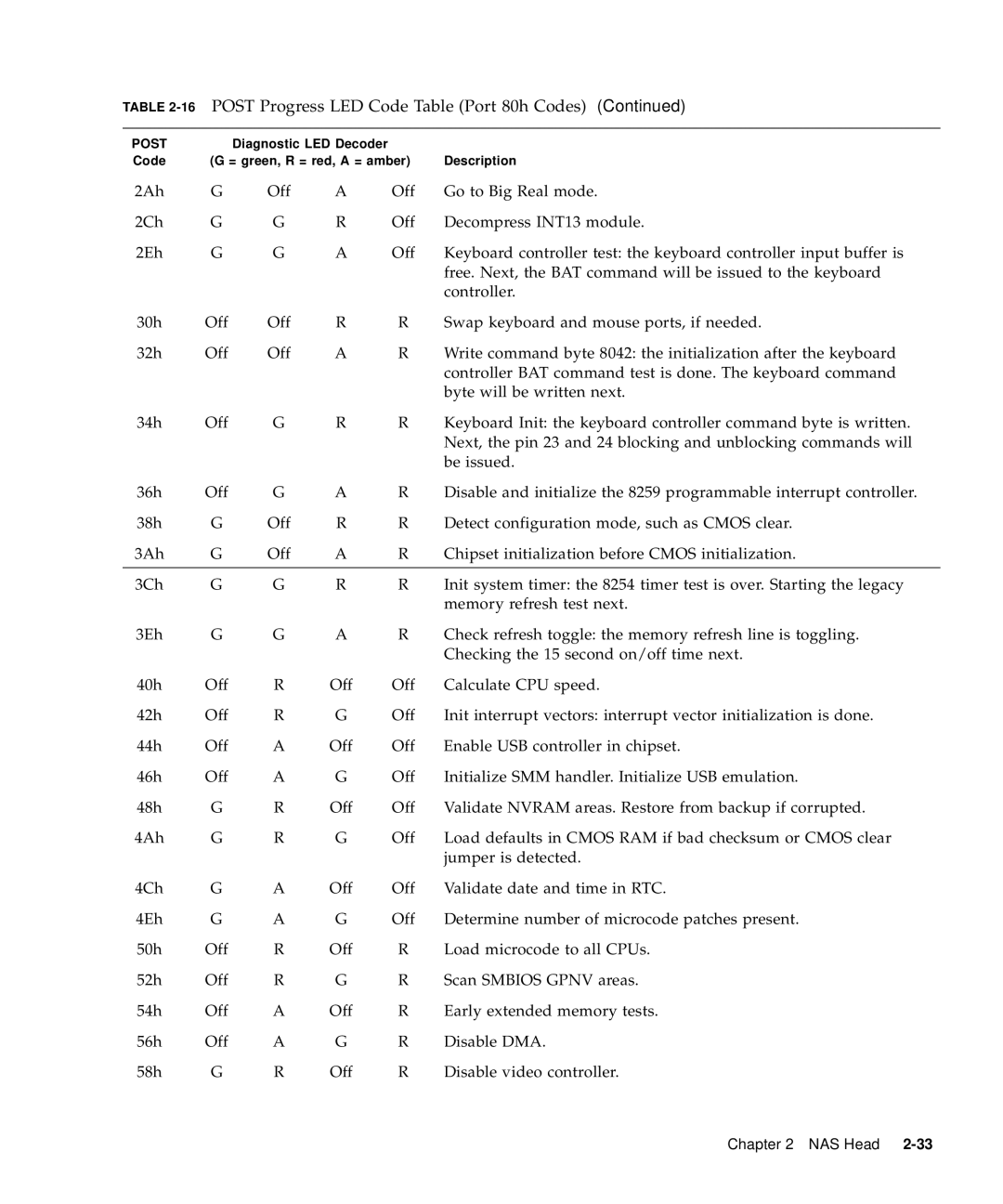

16POST Progress LED Code Table Port 80h Codes

Post Progress LED Code Table Port 80h Codes

34Sun StorEdge 5310 NAS Troubleshooting Guide December

Post Progress LED Code Table Port 80h Codes

OS Operations

Filesystem Check fsck Procedure

StorEdge Network Capture Utility

Upgrades Cacls Access Control List

Proc filesystem

Operating System

Updating the OS on the Sun StorEdge 5310 NAS

Sun StorEdge 5310 NAS Firmware

FTP Server

8The Update Software Panel

Common Problems Encountered on the Sun StorEdge 5310 NAS

CIFS/SMB/Domain

Cannot join Windows Domain

NAS Head

46Sun StorEdge 5310 NAS Troubleshooting Guide December

NAS Head

Reboot the StorEdge

Lost Connection with Windows Domain

50Sun StorEdge 5310 NAS Troubleshooting Guide December

StorEdge has same files in 2 different shares

Can’t map drives via CIFS/SMB

Can’t copy greater than 4G file from Windows to StorEdge

Cannot see the security tab from Windows clients

At the CLI, enter set smb.dirsymlink.disable yes

CIFS/SMB share created to /cvol is not visible or accessible

56Sun StorEdge 5310 NAS Troubleshooting Guide December

Users from trusted domains cannot access StorEdge

Dial-up CIFS/SMB clients cannot connect to StorEdge

Connection to Samba domain controller fails

Log Message Share database corrupt

Windows local groups cannot be added to Access Control List

Can’t create new DTQ

NFS root user doesnt have appropriate access

NFS Issues

Trusted host does not have root access

Local NIS files are no longer updating

64Sun StorEdge 5310 NAS Troubleshooting Guide December

NAS Head

When is it necessary to add a TCP/IP route?

Network Issues

How do I manually add a TCP/IP route?

NIC speed and duplex negotiation issues

How can I disable RIP routing?

Default gateway changes without user input

StorEdge is only reachable from systems on the local subnet

File system inaccessible mount failure

File System Issues

Can’t write to file system

File system related error messages

NAS Head

Light on one of the hard drives is red

Drive Failure Messages

Log message LUN critical Email alert LUN critical

Drive has failed how do I replace it?

Free space not immediately available after delete

File and Volume Operations

Can’t delete a file

After deleting files, volume free space remains the same

Can’t delete files from /etc directory

Cant run StorEdge Web Admin or some screens incorrect

Administration Interfaces

Cant run GUI, Java certificate expired message

Web GUI login failure

StorEdge Web Admin missing Icons or GUI does not respond

How do I reset the StorEdge administrator password?

Web GUI session aborted while performing administration

NAS Head

Load unixtools Ll /cvol

StorEdge Features and Utilities

StorEdge fails to send diagnostic email

Hardware Warning Messages

UPS Messages

Log message Low Battery

Log message Controller write-back cache is enabled

Log Message Blower Fan has failed

Light on one of the power supplies is amber

Front LCD panel message P21 Power 1 Failed

17Status LED Indicators

What do the Status LED Indicators on front panel indicate?

Network backup fails due to .attic$ directory

Backup Issues

Tape library not recognized

Ndmp Can’t browse backup history

Ndmp backup fails access denied message

Ndmp incremental/differential backups back up all files

Direct Attached Tape Libraries

Ndmp Can?t browse backup history

Local backup or restore fails with ?PNReduce error? in log

CIFS/SMB/Domain Issues

Frequently Asked Questions

How do I configure local SMB groups?

NAS Head

94Sun StorEdge 5310 NAS Troubleshooting Guide December

How do I create hidden shares?

What does the umask setting do?

NAS Head

How do I modify existing user and group credential mappings?

NAS Head

How do I set up the SMB Autohome directory feature?

NAS Head

102Sun StorEdge 5310 NAS Troubleshooting Guide December

Does StorEdge support Domain Local Groups?

What are the limitations of Workgroup mode?

What support is there for Windows Server Manager?

24 NIS/NIS+ Issues

How do I set up NIS or NIS+?

Does StorEdge support DFS?

How do I configure the NS lookup order?

What is port aggregation?

25 TCP/IP and Network Configuration

How do I disable port aggregation?

How do I set up port aggregation?

How do I set up IP aliasing?

What is IP aliasing?

How do I configure Jumbo Frames support?

Quota Configuration

Can I set more than one default gateway?

110Sun StorEdge 5310 NAS Troubleshooting Guide December

How do I configure user and group quotas at the CLI?

NAS UI

How do I set up Directory Tree Quotas DTQs?

Dtq remove volume=volume-name name=dtq-name

How do I create a DTQ for an existing directory?

How do I disable quotas?

How does the default quota work?

Checkpoint Configuration

What are checkpoints?

How do I set up checkpoints?

Select option 7, Save Changes or press Esc to cancel

How do I disable checkpoints?

How do I manage checkpoints from the command line?

How do I recover deleted files from a checkpoint?

How do I create a volume?

Volume Creation and Expansion

How do I extend the size of an existing volume?

How do I delete an existing volume?

How do I rename an existing volume?

Reserved Filesystems and Directories

What is the function of the .attic$ directory?

What is the function of the /etc directory?

What is the function of the /proc volume?

What is the function of the /dvol volume?

What is the function of the /cvol volume?

How do I share files with NFS users?

Select option M, Trusted Hosts

How do I manage NFS exports via the StorEdge Web Admin?

Object type path hosts or groups security

How do I manage NFS exports via the configuration files?

How do I access the StorEdge administration interfaces?

Administration Interfaces and Utilities

How do I collect diagnostics from StorEdge?

How do I set up Smtp email?

How do I set up local or remote logging?

132Sun StorEdge 5310 NAS Troubleshooting Guide December

How do I set up NTP or RDATE?

How can I capture network traffic to and from the StorEdge?

How do I access command history at the CLI?

136Sun StorEdge 5310 NAS Troubleshooting Guide December

SE5310 rm /vol1/dir1/file1

Rmdir /vol1/d1 /vol1/d2 /vol1/d3 /vol1

How do I configure the FTP service to load automatically?

How do I set up an FTP server on StorEdge?

How do I configure and secure rsh access?

Set rshd.allow.cmd.user yes

How do I access a shell prompt from the StorEdge CLI?

Backup and Migration Issues

NAS Head

What the best way to migrate data to or from StorEdge?

How do I set up Ndmp to backup the StorEdge?

How do I view the Ndmp backup log?

What does the desktop DB option in the shares menu do?

Macintosh Connectivity

How do I move files from one disk to another with NDMP?

How do I share files with Mac Users?

Miscellaneous Log Messages

System log message statmon error no statmon, remote

System log message ARP information overwritten

18Supported Tape Libraries and Tape Drives

Scsi ID Settings

What are the applications for File Replicator?

Disaster Recovery

StorEdge File Replicator

How Does File Replicator work?

How do I set up File Replicator?

Backup

Data Distribution

To activate Mirror License both systems, do the following

Enter the desired size of the Mirror Buffer

StorEdge File Replicator Issues

Waiting on host, link is down

Error Initializing mirror buffer

Mirror stops when creating buffer

Mirror Promoted on host

EXT Free Pages

Array Overview

Fibre Channel FC

Module Description

Controllers

Controller Battery

2Label Locations on the Controller

Controller Memory

Drives

3Battery Charging/Charged and Cache Active Lights

5Drive Numbering Rackmount Module

Fans

SFP Transceivers and Cables

Power Supplies

8SFP Transceiver and fibre Optic Cable

Tray ID Switch

Removing and Replacing the Back Cover

Using the Array

10Removing and Replacing a Deskside Module Back Cover

Turning On the Power

Check the status of each module and it components

Turning Off Power for a Planned Shutdown

12Sun StorEdge 5310 NAS Troubleshooting Guide December

12and -1shows the locations of the status lights

1Lights on the Back of a Command Module

Fan Fault Amber Off Replacing Fan on

Turning Off Power for an Unplanned Shutdown

Storage Arrays

Restoring Power After an Unplanned Shutdown

Yes Go to step No Go to step

13Alarm Mute Button

Responding to the Optional Audible Alarm

Yes Go to . No Go to step

Troubleshooting the Module

Troubleshooting and Recovery

Storage Arrays

Lights on the Back of a Command Module

3Lights on the Back of a Command Module

Recovering from an Overheated Power Supply

Did the power supplies restart automatically?

16Power Supply Switches

17shows the location of the Tray ID switch

Setting the Tray ID Switch

17Setting the Tray ID Switch

Verifying the Link Rate Setting

Upgrade Requirements

Relocating a Command Module

Adding New Drives

Upgrade Methods

Replace Existing Drives with Greater Capacity Drives

Replace All Drives at the Same Time

Adding New Drives to Empty Slots

Replace One Drive at a Time

Locate the blank drives in the command module

Repeat and to install each new drive

Put on antistatic protection Unpack the new drives

Replacing All Drives at the Same Time

Yes- Go to . No Go to step

20Power Supply Switches

Replacing One Drive at a Time

Put on antistatic protection Unpack the new drives

Yes- Go to . No Go to step

22Removing and Installing a Drive

Relocate Drives or Modules

Relocation Considerations

Raid Storage Manager RSM

Convert an Command Module to a Drive Module

23Enterprise Management Window

Client Software Windows

25Enterprise Management Window

Enterprise Management Window

26Device Tree Example

Device Tree

Enterprise Management Window Menus

Device Table

4Enterprise Management Window Menus

Enterprise Management Window Toolbar

Array Management Window

5Enterprise Management Window Toolbar Buttons

Array Management Window Tabs

27Array Management Window

6Array Management Window Tabs

Array Management Window Menus

7Array Management Window Menus 1

8Array Management Window Toolbar Buttons

Array Management Window Toolbar

Software Redundancy

Protecting Your Data

RAID Levels and Data Redundancy

Volume Copy

Remote Volume Mirroring

Snapshot Volumes

Storage Arrays

9RAID Level Configurations

RAID

Controller Cache Memory

Hardware Redundancy

Background Media Scan

Hot Spare Drives

6.8 I/O Data Path Protection

Multi-Path Driver with AVT Enabled

Channel Protection

Multi-Path Driver with AVT Disabled

Password Protection

Volumes and Volume Groups

Configuring Storage Arrays

Password Failure Reporting and Lockout

Volume Groups

28Unconfigured and Free Capacity Nodes

Standard Volumes

Specifying Volume Parameters from Unconfigured Capacity

Specifying Volume Parameters from Free Capacity

29Mappings View Window

Mappings View

10Mappings View Tab

11Volume-to-LUN Terminology

70Sun StorEdge 5310 NAS Troubleshooting Guide December

Register the Volume with the Operating System

SANshare Storage Partitioning Example

SANshare Storage Partitioning

SANshare Storage Partitioning involves three key steps

Heterogeneous Hosts

31Host Port Definitions Dialog

Heterogeneous Hosts Example

32Heterogeneous Hosts Example

Storage Arrays

Dynamic Volume Expansion DVE

33DVE Modification Operation in Progress

80Sun StorEdge 5310 NAS Troubleshooting Guide December

Data Replication

82Sun StorEdge 5310 NAS Troubleshooting Guide December

34Persistent Reservations Dialog

Managing Persistent Reservations

Storage Array Health

Maintaining and Monitoring Storage Arrays

Storage Array Status Icons

12Storage Array Status Icon Quick Reference

Event Monitor

36Event Monitor Configuration

37Event Monitor Example

Storage Arrays

Problem Notification

38Problem Notification in the Array Management Window

Storage Array Problem Recovery

39Displaying the Recovery Guru Window

40Recovery Guru Window Example

41Status Changes During an Example Recovery Operation

Updating Firmware and Nvsram on the Array

Start the SMclient

Storage Arrays

Example, c\temp\rsmfw\ Select N2882-610843-5xx.dlp

Updating ESM Firmware

Select Start to begin the upgrade

Overview

StorEdge File Replicator

NBD

1Standard Terms

Pseudo Real-time Mirroring

Real-time Mirroring

StorEdge File Replicator

1The lifecycle of a transaction in StorEdge File Replicator

2Write ordering on the Mirror

3Lost transaction handling on the Mirror

Many-to-One Mirroring

Mirroring Variations

Piggyback or Cascading Mirroring

One-to-Many Mirroring

Push Technology

Operational State

Bi-directional Mirroring

Replication

Mirror Creation

Mirror Replication

Link Down and Idle Conditions

Mirror Sequencing

Cracked and Broken Mirrors

Cannot perform first-time synchronization of mirror system

Filesystem errors, such as run check, directory broken, etc

14Sun StorEdge 5310 NAS Troubleshooting Guide December

Clustering

2Sun StorEdge 5310 NAS Troubleshooting Guide December

Checkpoints/Snapshots

Volumes

Physical and Logical Volume Relationship

Checkpoint Creation

Checkpoint Lifecycle

2The Copy-On-Write Mechanism for Checkpoints

Active Checkpoint

3Mappings for Block n Before Modification

4Mappings for Block n After Modification

Translation of File System Objects in Checkpoints

Src directory entry

Src inode nlink =

Entry Dst directory entry Src inode nlink = Entry y

Checkpoint Deletion

6Mappings for Block n After Deleting ckpti-1

Local Directory Checkpoint Access

Checkpoint management commands

Checkpoint Scheduling

Accessing Checkpointed Data

8Accessing .chkpnt in Unix

Syntax for the command is

Compatibility Issues

9Accessing .chkpnt in Windows Explorer

10Viewing .chkpnt in Windows Explorer

Object Checkpoint Restore

11Sharing Blocks Between Live and Checkpoint File Systems

StorEdge cp Command

18Sun StorEdge 5310 NAS Troubleshooting Guide December

Checkpoints/Snapshots

20Sun StorEdge 5310 NAS Troubleshooting Guide December

Tools and Supplies Needed

FRU/CRU Replacement Procedures

Safety Before You Remove the Cover

Determining a Faulty Component

Removing and Replacing the Cover

Set the cover aside and away from the immediate work area

NAS Head FRU Replacement Procedures

Field Replaceable Unit FRU Procedures

Opening the Front Bezel

2Sun StorEdge 5310 NAS Bezel Replacement

3Sun StorEdge 5310 NAS Expansion Unit

Memory

Sun StorEdge 5310 NAS Power Supply

Power Supply Unit

4Replacing the Power Supply

Sun StorEdge 5310 NAS Fan Module Removal

Fan Module

5Removing the Fan Module

Sun StorEdge 5310 NAS Fan Module Replacement

High Profile Riser PCI Cards

Gigabit Ethernet Card

6The Gigabit Ethernet Card in the Low Profile Riser Slot

Low Profile Riser PCI Cards

Qlogic HBA Removal and Replacement

LCD Display Module

Flash Disk Module

Backup of /dvol/etc

Replacing the Flash Disk

Flash Disk

Upgrade and Configuration Recovery

Reboot the server to complete the upgrade process

System FRU Super FRU

Super FRU Installation

Replacing a Controller

Array FRU replacement Procedures

Tools and Equipment

Procedure

FRU/CRU Replacement Procedures

Are you using the battery from the old controller?

12Replacing the Controller Battery

13Label Locations for the Controller

14Controller Host Link, Drive Link, and Fault Lights

Replacing a Controller Battery

Procedure

15Removing the SFP Transceiver and fibre Optic Cable

Date of Installation Enter todays date

17Removing the Controller Cover Upside Down View

19Label Locations on the Controller

Is the problem corrected?

Replacing a Drive

20Drive Link, Host Link, Battery, and Fault Lights

FRU/CRU Replacement Procedures

21Replacing a Drive

Replacing a Fan

22Replacing a Fan

Replacing a Power Supply

42Sun StorEdge 5310 NAS Troubleshooting Guide December

Check the Power and Fault light on the new power supply

Replacing an SFP Transceiver

24Replacing an SFP Transceiver

Yes Go to step No Contact technical support