Advanced Version | |

400 MHz CPU, 4.0 MB |

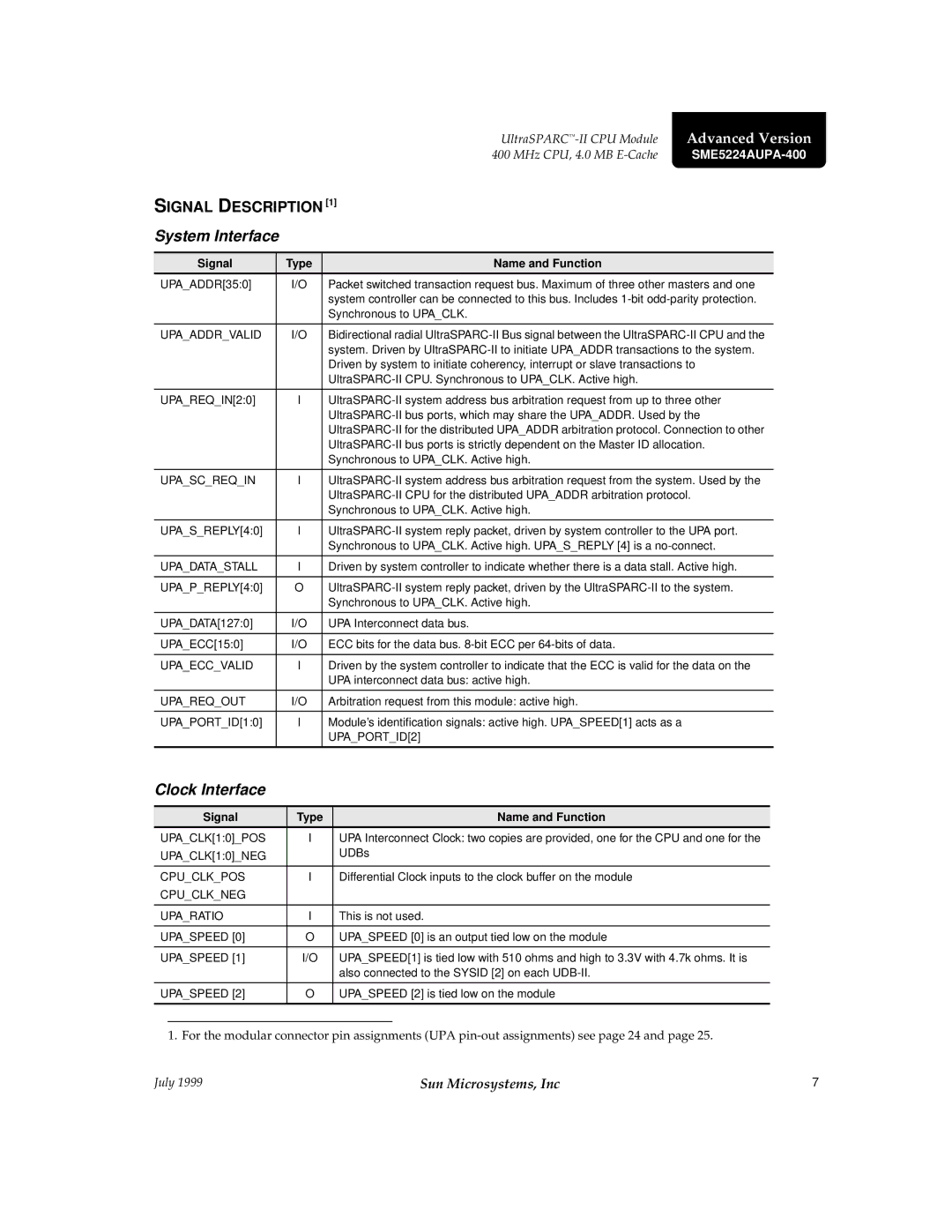

SIGNAL DESCRIPTION [1]

System Interface

Signal | Type | Name and Function |

UPA_ADDR[35:0] | I/O | Packet switched transaction request bus. Maximum of three other masters and one |

|

| system controller can be connected to this bus. Includes |

|

| Synchronous to UPA_CLK. |

|

|

|

UPA_ADDR_VALID | I/O | Bidirectional radial |

|

| system. Driven by |

|

| Driven by system to initiate coherency, interrupt or slave transactions to |

|

| |

|

|

|

UPA_REQ_IN[2:0] | I | |

|

| |

|

| |

|

| |

|

| Synchronous to UPA_CLK. Active high. |

|

|

|

UPA_SC_REQ_IN | I | |

|

| |

|

| Synchronous to UPA_CLK. Active high. |

|

|

|

UPA_S_REPLY[4:0] | I | |

|

| Synchronous to UPA_CLK. Active high. UPA_S_REPLY [4] is a |

|

|

|

UPA_DATA_STALL | I | Driven by system controller to indicate whether there is a data stall. Active high. |

|

|

|

UPA_P_REPLY[4:0] | O | |

|

| Synchronous to UPA_CLK. Active high. |

|

|

|

UPA_DATA[127:0] | I/O | UPA Interconnect data bus. |

|

|

|

UPA_ECC[15:0] | I/O | ECC bits for the data bus. |

|

|

|

UPA_ECC_VALID | I | Driven by the system controller to indicate that the ECC is valid for the data on the |

|

| UPA interconnect data bus: active high. |

|

|

|

UPA_REQ_OUT | I/O | Arbitration request from this module: active high. |

|

|

|

UPA_PORT_ID[1:0] | I | Module’s identification signals: active high. UPA_SPEED[1] acts as a |

|

| UPA_PORT_ID[2] |

|

|

|

Clock Interface

Signal | Type | Name and Function |

UPA_CLK[1:0]_POS | I | UPA Interconnect Clock: two copies are provided, one for the CPU and one for the |

UPA_CLK[1:0]_NEG |

| UDBs |

|

|

|

CPU_CLK_POS | I | Differential Clock inputs to the clock buffer on the module |

CPU_CLK_NEG |

|

|

|

|

|

UPA_RATIO | I | This is not used. |

|

|

|

UPA_SPEED [0] | O | UPA_SPEED [0] is an output tied low on the module |

|

|

|

UPA_SPEED [1] | I/O | UPA_SPEED[1] is tied low with 510 ohms and high to 3.3V with 4.7k ohms. It is |

|

| also connected to the SYSID [2] on each |

|

|

|

UPA_SPEED [2] | O | UPA_SPEED [2] is tied low on the module |

|

|

|

1. For the modular connector pin assignments (UPA

July 1999 | Sun Microsystems, Inc | 7 |