TMS320C6201 Silicon Errata | SPRZ153 |

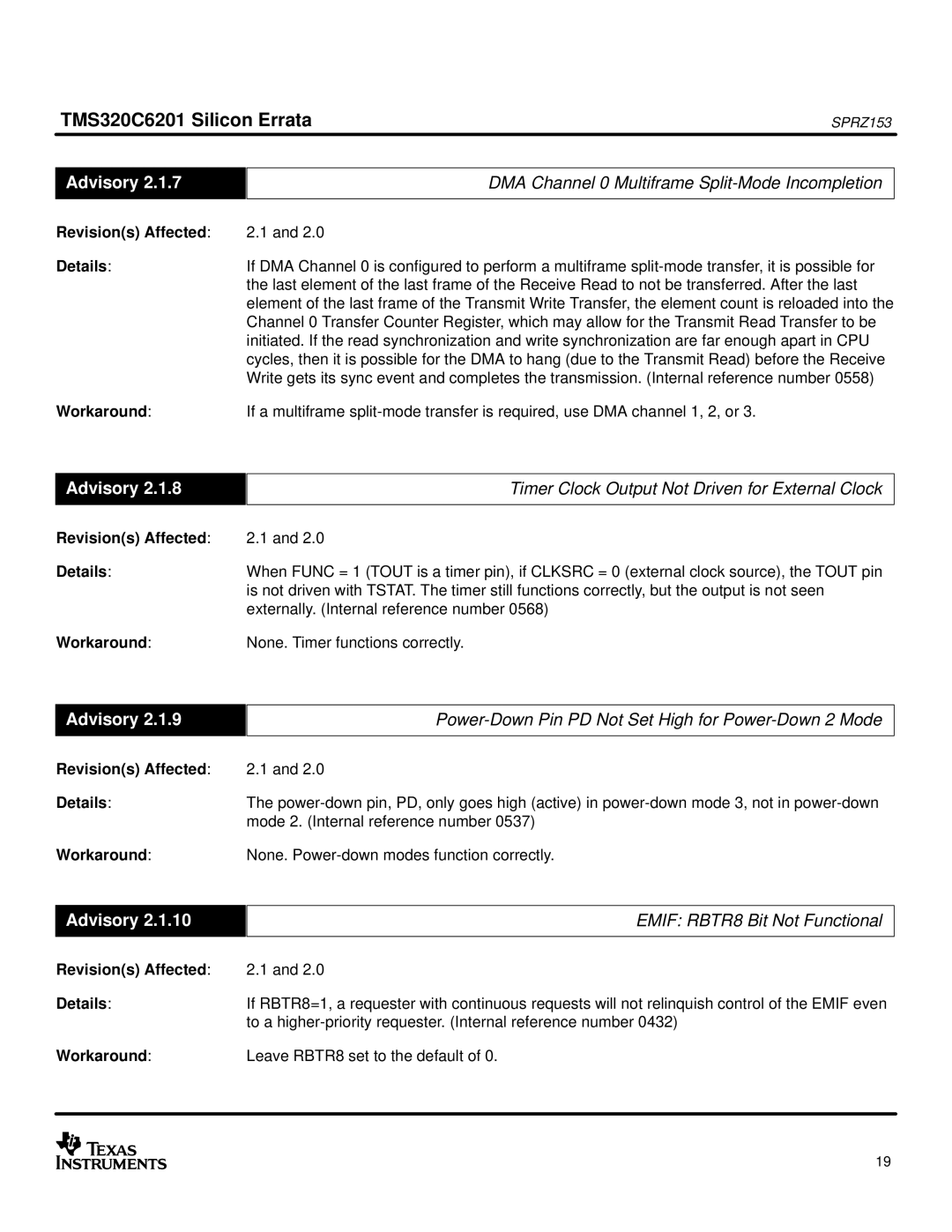

Advisory 2.1.7

DMA Channel 0 Multiframe Split-Mode Incompletion

Revision(s) Affected:

Details:

Workaround:

Advisory 2.1.8

Revision(s) Affected:

Details:

Workaround:

Advisory 2.1.9

Revision(s) Affected:

Details:

Workaround:

Advisory 2.1.10

Revision(s) Affected:

Details:

Workaround:

2.1 and 2.0

If DMA Channel 0 is configured to perform a multiframe

If a multiframe

Timer Clock Output Not Driven for External Clock

2.1 and 2.0

When FUNC = 1 (TOUT is a timer pin), if CLKSRC = 0 (external clock source), the TOUT pin is not driven with TSTAT. The timer still functions correctly, but the output is not seen externally. (Internal reference number 0568)

None. Timer functions correctly.

Power-Down Pin PD Not Set High for Power-Down 2 Mode

2.1 and 2.0

The

None.

EMIF: RBTR8 Bit Not Functional

2.1 and 2.0

If RBTR8=1, a requester with continuous requests will not relinquish control of the EMIF even to a

Leave RBTR8 set to the default of 0.

19