TMS320C6201 Silicon Errata | SPRZ153 |

2Changes to the TMS320C6201 Data Sheet (literature number SPRS051)

Table 2. Timing Requirements for Interrupt Response Cycles

NO. |

|

| C6201B | UNIT | |

|

|

|

| ||

|

| MIN | MAX | ||

|

|

|

| ||

|

|

|

|

|

|

4 | Delay time, CLKOUT2 low to IACK valid | 6 | ns | ||

5 | Delay time, CLKOUT2 low to INUMx valid |

| 6 | ns | |

6 | Delay time, CLKOUT2 low to INUMx invalid |

| ns | ||

Table 3. JTAG Test-Port Timing

|

|

|

|

| C6201, |

| |

NO. |

|

|

|

| C6201B | UNIT | |

|

|

|

|

|

| ||

|

|

|

|

| MIN | MAX |

|

|

|

|

|

|

|

|

|

1 | Tc(TCK) | Cycle time, TCK | 50 |

| ns | ||

4 |

|

|

|

|

|

| |

Hold time, TDI/TMS/TRST | valid after TCK high | 9 |

| ns | |||

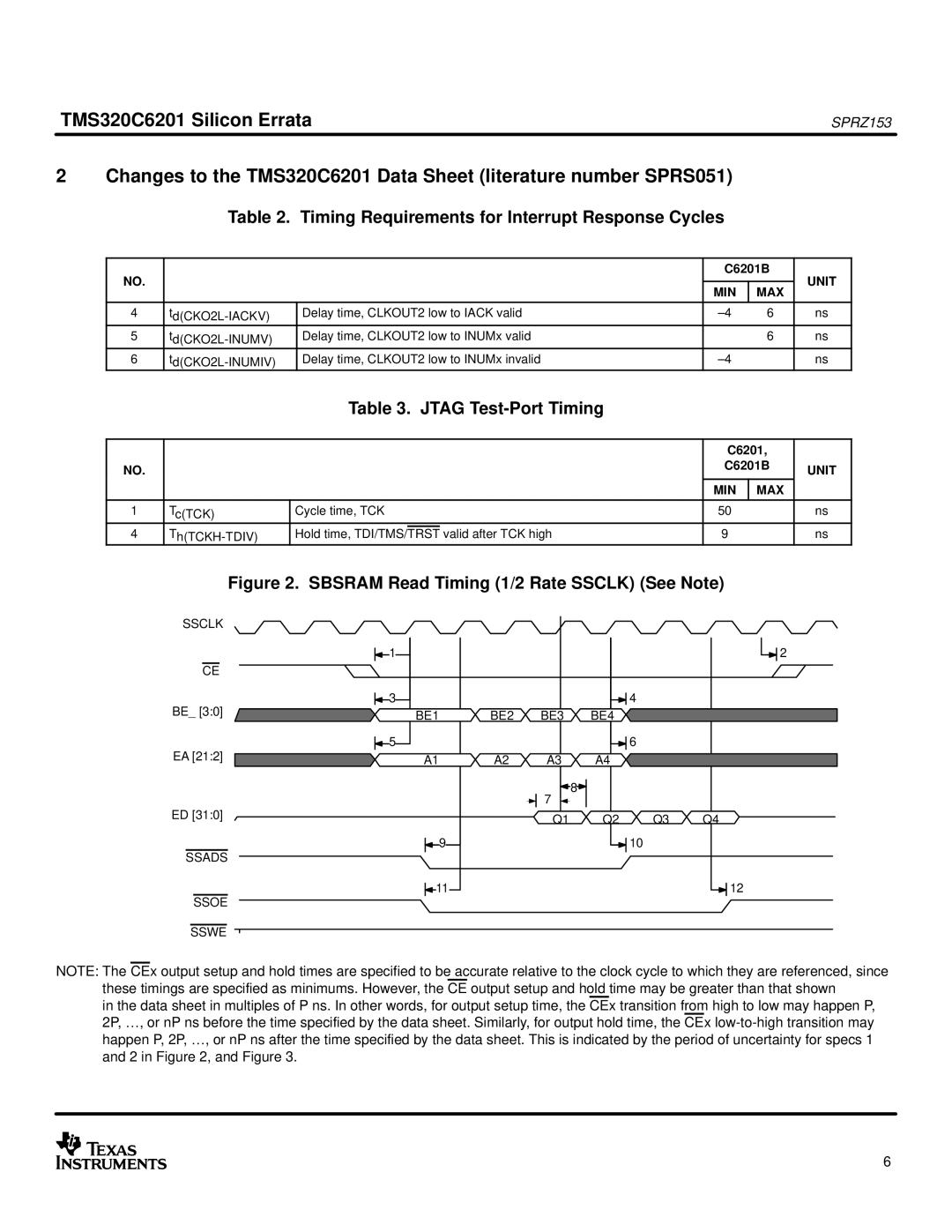

Figure 2. SBSRAM Read Timing (1/2 Rate SSCLK) (See Note)

SSCLK

![]() 1

1

CE

![]() 3

3

BE_ [3:0]

![]() 5

5

EA [21:2]

ED [31:0]

SSADS

SSOE

SSWE

BE1

A1

![]() 9

9

![]() 11

11

![]()

![]() 2

2

|

|

| 4 |

|

BE2 | BE3 | BE4 |

|

|

|

|

| 6 |

|

A2 | A3 | A4 |

|

|

| 7 | 8 |

|

|

|

|

|

| |

| Q1 | Q2 | Q3 | Q4 |

|

|

| 10 |

|

![]() 12

12

NOTE: The CEx output setup and hold times are specified to be accurate relative to the clock cycle to which they are referenced, since these timings are specified as minimums. However, the CE output setup and hold time may be greater than that shown

in the data sheet in multiples of P ns. In other words, for output setup time, the CEx transition from high to low may happen P, 2P, … , or nP ns before the time specified by the data sheet. Similarly, for output hold time, the CEx

6