TMS320C6201 Silicon Errata | SPRZ153 |

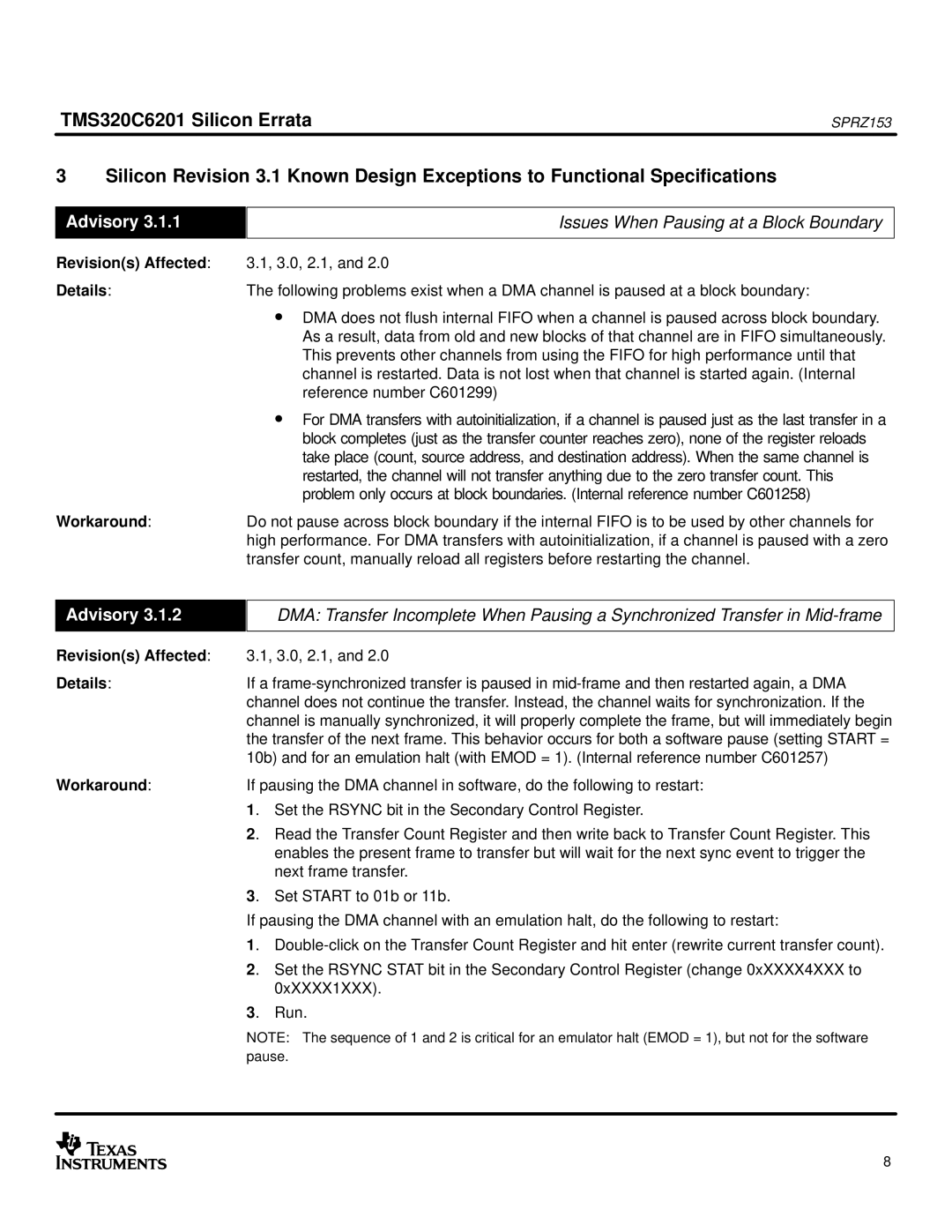

3 Silicon Revision 3.1 Known Design Exceptions to Functional Specifications

Advisory 3.1.1

Revision(s) Affected:

Details:

Workaround:

Issues When Pausing at a Block Boundary

3.1, 3.0, 2.1, and 2.0

The following problems exist when a DMA channel is paused at a block boundary:

•DMA does not flush internal FIFO when a channel is paused across block boundary. As a result, data from old and new blocks of that channel are in FIFO simultaneously. This prevents other channels from using the FIFO for high performance until that channel is restarted. Data is not lost when that channel is started again. (Internal reference number C601299)

•For DMA transfers with autoinitialization, if a channel is paused just as the last transfer in a block completes (just as the transfer counter reaches zero), none of the register reloads take place (count, source address, and destination address). When the same channel is restarted, the channel will not transfer anything due to the zero transfer count. This problem only occurs at block boundaries. (Internal reference number C601258)

Do not pause across block boundary if the internal FIFO is to be used by other channels for high performance. For DMA transfers with autoinitialization, if a channel is paused with a zero transfer count, manually reload all registers before restarting the channel.

Advisory 3.1.2

Revision(s) Affected:

Details:

Workaround:

DMA: Transfer Incomplete When Pausing a Synchronized Transfer in

3.1, 3.0, 2.1, and 2.0

If a

If pausing the DMA channel in software, do the following to restart:

1. Set the RSYNC bit in the Secondary Control Register.

2. Read the Transfer Count Register and then write back to Transfer Count Register. This enables the present frame to transfer but will wait for the next sync event to trigger the next frame transfer.

3. Set START to 01b or 11b.

If pausing the DMA channel with an emulation halt, do the following to restart:

1.

2. Set the RSYNC STAT bit in the Secondary Control Register (change 0xXXXX4XXX to 0xXXXX1XXX).

3. Run.

NOTE: The sequence of 1 and 2 is critical for an emulator halt (EMOD = 1), but not for the software pause.

8