TMS320C6201 Silicon Errata | SPRZ153 |

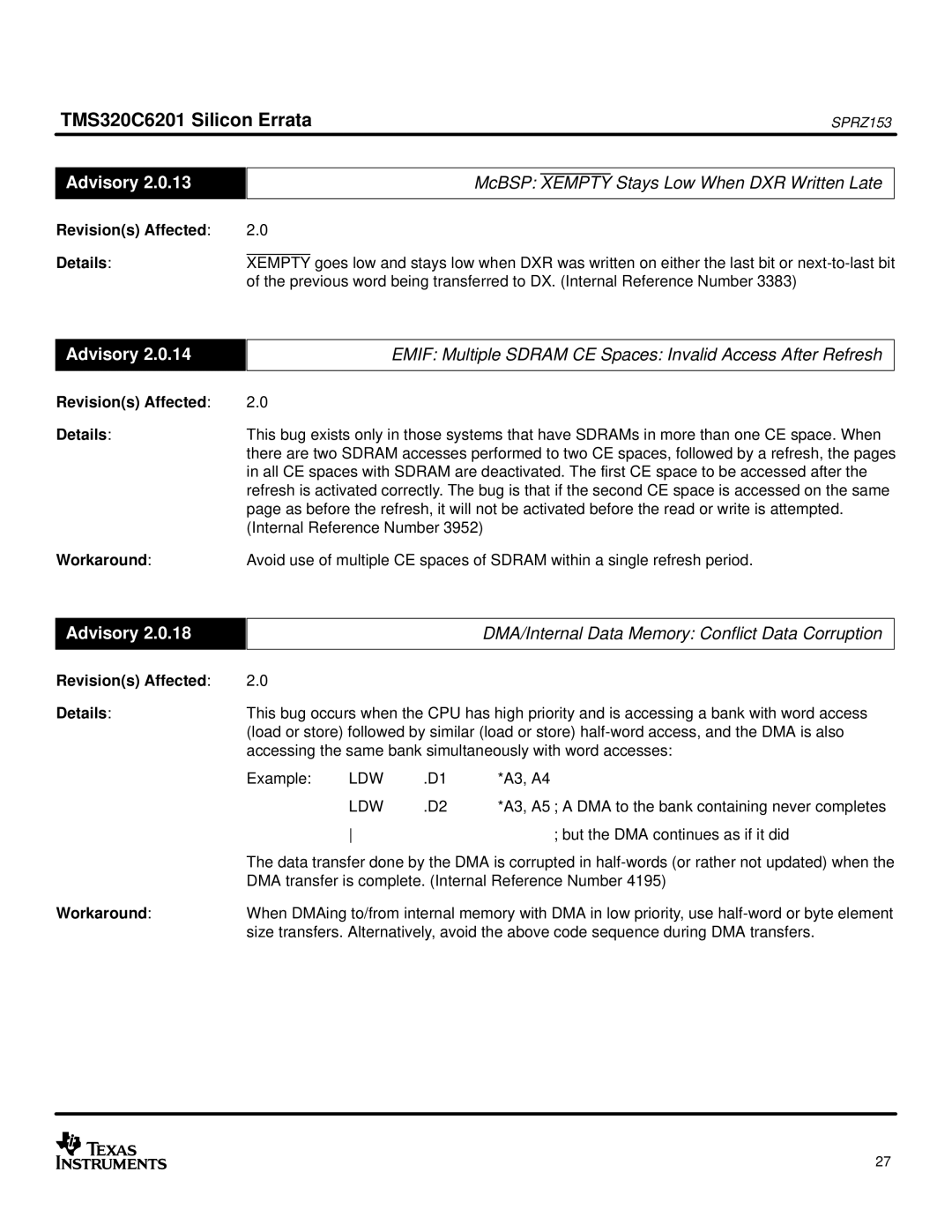

Advisory 2.0.13

Revision(s) Affected:

Details:

Advisory 2.0.14

Revision(s) Affected:

Details:

Workaround:

Advisory 2.0.18

Revision(s) Affected:

Details:

Workaround:

McBSP: XEMPTY Stays Low When DXR Written Late

2.0

XEMPTY goes low and stays low when DXR was written on either the last bit or

EMIF: Multiple SDRAM CE Spaces: Invalid Access After Refresh

2.0

This bug exists only in those systems that have SDRAMs in more than one CE space. When there are two SDRAM accesses performed to two CE spaces, followed by a refresh, the pages in all CE spaces with SDRAM are deactivated. The first CE space to be accessed after the refresh is activated correctly. The bug is that if the second CE space is accessed on the same page as before the refresh, it will not be activated before the read or write is attempted. (Internal Reference Number 3952)

Avoid use of multiple CE spaces of SDRAM within a single refresh period.

DMA/Internal Data Memory: Conflict Data Corruption

2.0

This bug occurs when the CPU has high priority and is accessing a bank with word access (load or store) followed by similar (load or store)

Example: | LDW | .D1 | *A3, A4 |

|

| LDW | .D2 | *A3, A5 | ; A DMA to the bank containing never completes |

|

|

| ; but the DMA continues as if it did |

The data transfer done by the DMA is corrupted in

When DMAing to/from internal memory with DMA in low priority, use

27