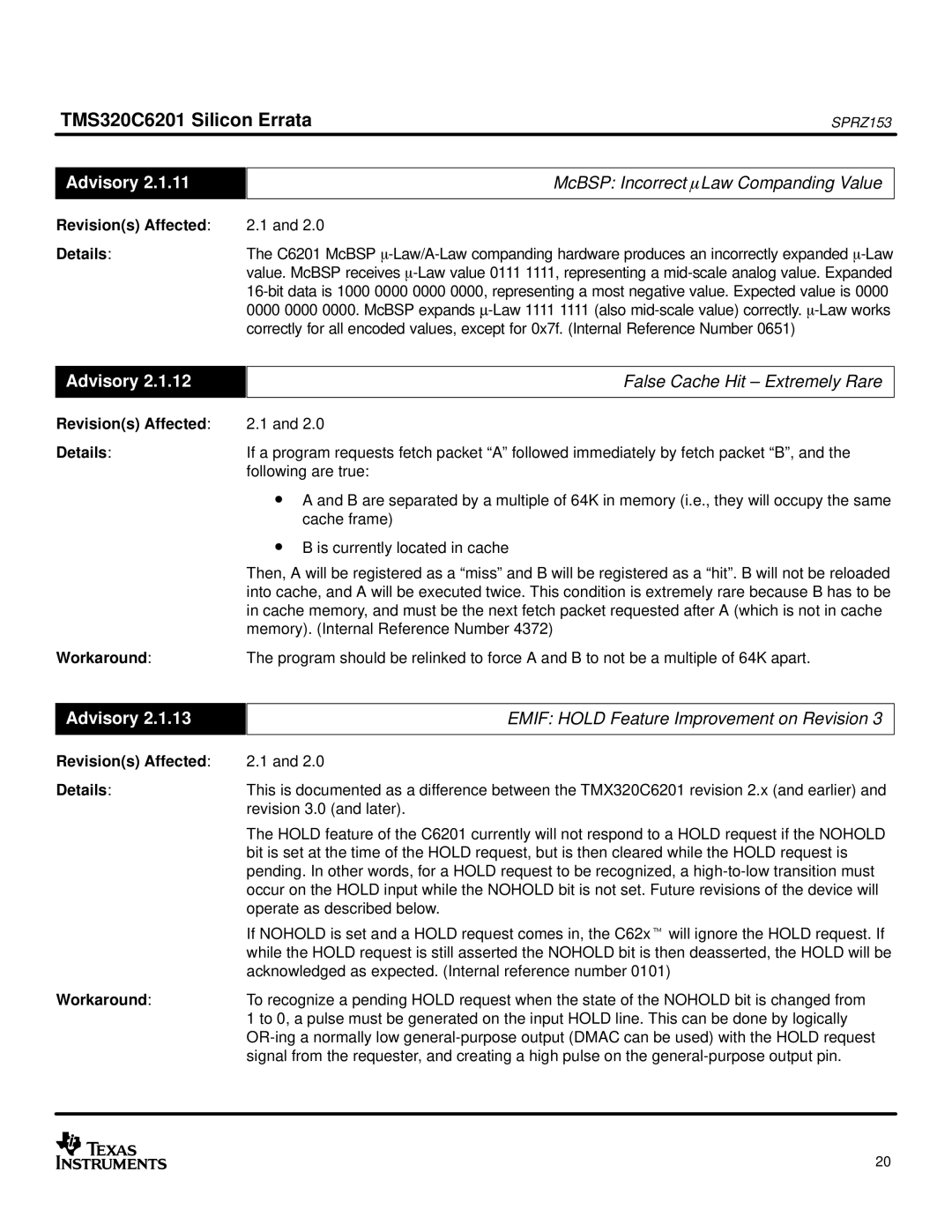

TMS320C6201 Silicon Errata | SPRZ153 |

Advisory 2.1.11

Revision(s) Affected:

Details:

McBSP: Incorrect mLaw Companding Value

2.1 and 2.0

The C6201 McBSP

Advisory 2.1.12

Revision(s) Affected:

Details:

Workaround:

Advisory 2.1.13

Revision(s) Affected:

Details:

Workaround:

False Cache Hit – Extremely Rare

2.1 and 2.0

If a program requests fetch packet “A” followed immediately by fetch packet “B”, and the following are true:

•A and B are separated by a multiple of 64K in memory (i.e., they will occupy the same cache frame)

•B is currently located in cache

Then, A will be registered as a “miss” and B will be registered as a “hit”. B will not be reloaded into cache, and A will be executed twice. This condition is extremely rare because B has to be in cache memory, and must be the next fetch packet requested after A (which is not in cache memory). (Internal Reference Number 4372)

The program should be relinked to force A and B to not be a multiple of 64K apart.

EMIF: HOLD Feature Improvement on Revision 3

2.1 and 2.0

This is documented as a difference between the TMX320C6201 revision 2.x (and earlier) and revision 3.0 (and later).

The HOLD feature of the C6201 currently will not respond to a HOLD request if the NOHOLD bit is set at the time of the HOLD request, but is then cleared while the HOLD request is pending. In other words, for a HOLD request to be recognized, a

If NOHOLD is set and a HOLD request comes in, the C62xt will ignore the HOLD request. If while the HOLD request is still asserted the NOHOLD bit is then deasserted, the HOLD will be acknowledged as expected. (Internal reference number 0101)

To recognize a pending HOLD request when the state of the NOHOLD bit is changed from 1 to 0, a pulse must be generated on the input HOLD line. This can be done by logically

20