TMS320C6201 Silicon Errata | SPRZ153 |

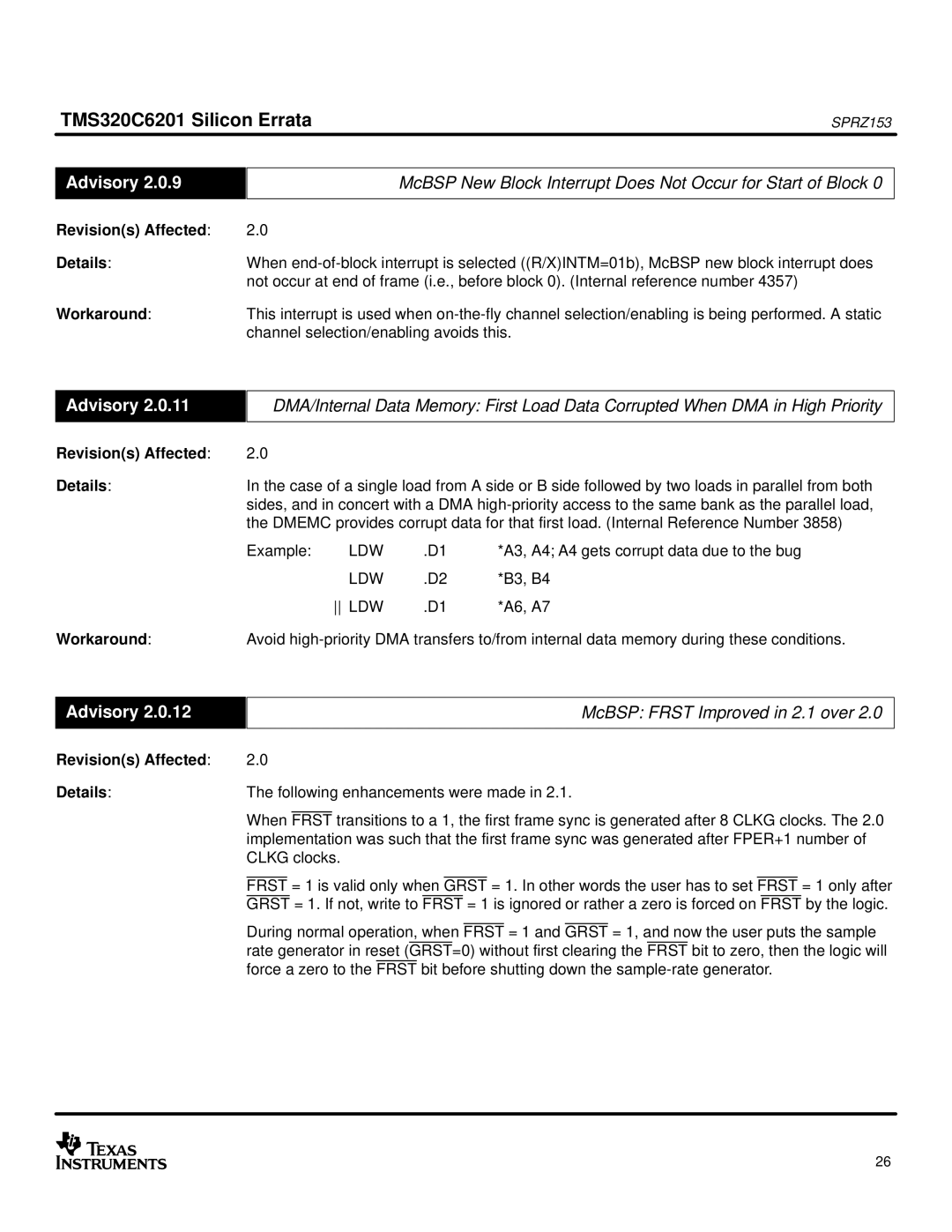

Advisory 2.0.9

Revision(s) Affected:

Details:

Workaround:

Advisory 2.0.11

Revision(s) Affected:

Details:

Workaround:

Advisory 2.0.12

Revision(s) Affected:

Details:

McBSP New Block Interrupt Does Not Occur for Start of Block 0

2.0

When

This interrupt is used when

DMA/Internal Data Memory: First Load Data Corrupted When DMA in High Priority

2.0

In the case of a single load from A side or B side followed by two loads in parallel from both sides, and in concert with a DMA

Example: | LDW | .D1 | *A3, A4; A4 gets corrupt data due to the bug |

| LDW | .D2 | *B3, B4 |

| LDW | .D1 | *A6, A7 |

Avoid

McBSP: FRST Improved in 2.1 over 2.0

2.0

The following enhancements were made in 2.1.

When FRST transitions to a 1, the first frame sync is generated after 8 CLKG clocks. The 2.0 implementation was such that the first frame sync was generated after FPER+1 number of CLKG clocks.

FRST = 1 is valid only when GRST = 1. In other words the user has to set FRST = 1 only after GRST = 1. If not, write to FRST = 1 is ignored or rather a zero is forced on FRST by the logic.

During normal operation, when FRST = 1 and GRST = 1, and now the user puts the sample rate generator in reset (GRST=0) without first clearing the FRST bit to zero, then the logic will force a zero to the FRST bit before shutting down the

26