bdiGDB for GNU Debugger, BDI2000 | User Manual | 45 | |||

|

|

|

| ||

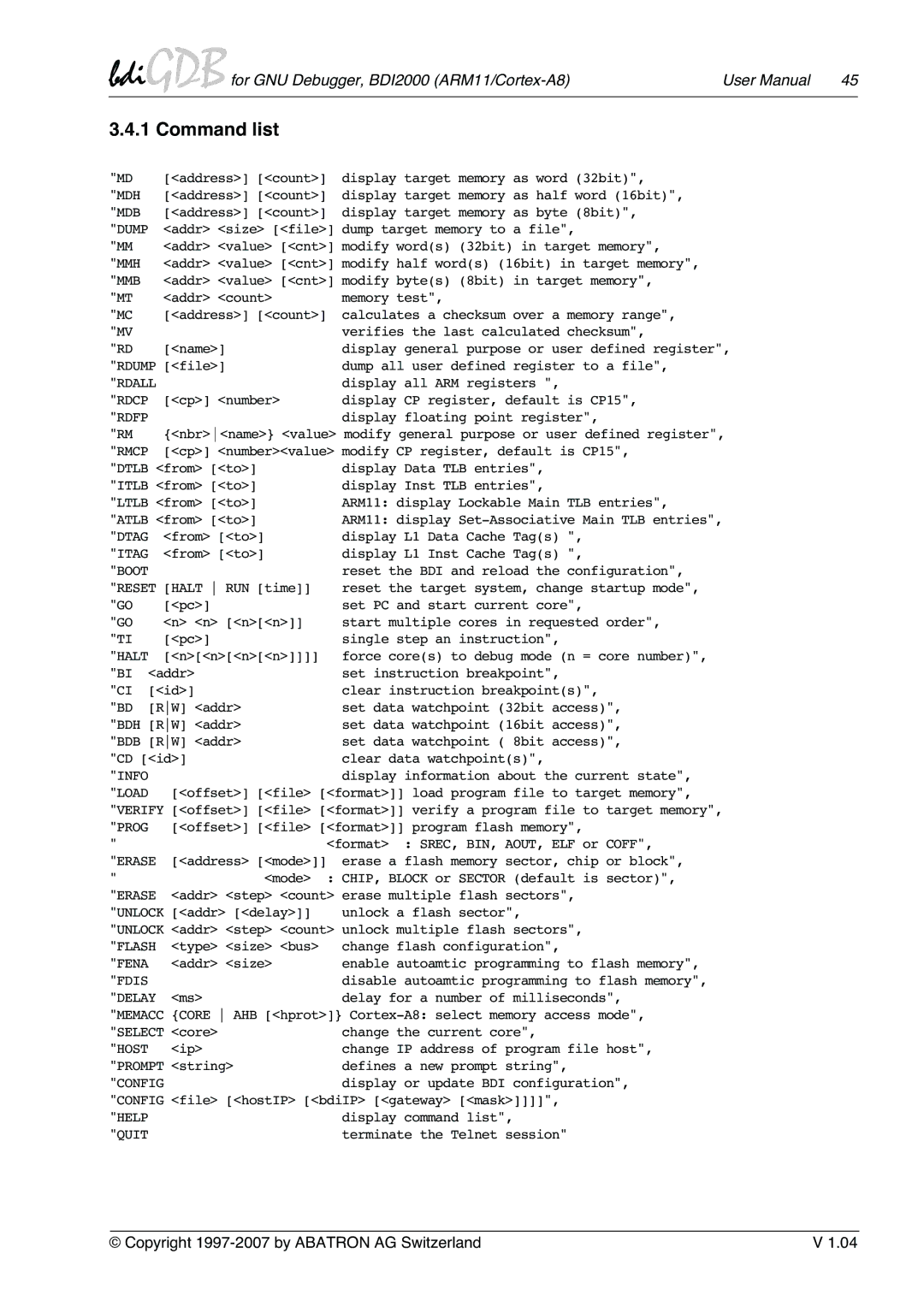

3.4.1 Command list |

|

|

| ||

"MD |

| [<address>] [<count>] | display target memory as word (32bit)", |

|

|

"MDH |

| [<address>] [<count>] | display target memory as half word (16bit)", |

|

|

"MDB |

| [<address>] [<count>] | display target memory as byte (8bit)", |

|

|

"DUMP | <addr> <size> [<file>] | dump target memory to a file", |

|

| |

"MM |

| <addr> <value> [<cnt>] | modify word(s) (32bit) in target memory", |

|

|

"MMH |

| <addr> <value> [<cnt>] | modify half word(s) (16bit) in target memory", |

|

|

"MMB |

| <addr> <value> [<cnt>] | modify byte(s) (8bit) in target memory", |

|

|

"MT |

| <addr> <count> | memory test", |

|

|

"MC |

| [<address>] [<count>] | calculates a checksum over a memory range", |

|

|

"MV |

|

| verifies the last calculated checksum", |

|

|

"RD |

| [<name>] | display general purpose or user defined register", |

| |

"RDUMP [<file>] | dump all user defined register to a file", |

|

| ||

"RDALL |

| display all ARM registers ", |

|

| |

"RDCP | [<cp>] <number> | display CP register, default is CP15", |

|

| |

"RDFP |

| display floating point register", |

|

| |

"RM |

| {<nbr> <name>} <value> modify general purpose or user defined register", |

| ||

"RMCP | [<cp>] <number><value> modify CP register, default is CP15", |

|

| ||

"DTLB <from> [<to>] | display Data TLB entries", |

|

| ||

"ITLB <from> [<to>] | display Inst TLB entries", |

|

| ||

"LTLB <from> [<to>] | ARM11: display Lockable Main TLB entries", |

|

| ||

"ATLB <from> [<to>] | ARM11: display |

| |||

"DTAG | <from> [<to>] | display L1 Data Cache Tag(s) ", |

|

| |

"ITAG | <from> [<to>] | display L1 Inst Cache Tag(s) ", |

|

| |

"BOOT |

| reset the BDI and reload the configuration", |

|

| |

"RESET [HALT RUN [time]] | reset the target system, change startup mode", |

|

| ||

"GO |

| [<pc>] | set PC and start current core", |

|

|

"GO |

| <n> <n> [<n>[<n>]] | start multiple cores in requested order", |

|

|

"TI |

| [<pc>] | single step an instruction", |

|

|

"HALT | [<n>[<n>[<n>[<n>]]]] | force core(s) to debug mode (n = core number)", |

|

| |

"BI | <addr> | set instruction breakpoint", |

|

| |

"CI | [<id>] | clear instruction breakpoint(s)", |

|

| |

"BD | [RW] <addr> | set data watchpoint (32bit access)", |

|

| |

"BDH [RW] <addr> | set data watchpoint (16bit access)", |

|

| ||

"BDB [RW] <addr> | set data watchpoint ( 8bit access)", |

|

| ||

"CD [<id>] | clear data watchpoint(s)", |

|

| ||

"INFO |

| display information about the current state", |

|

| |

"LOAD | [<offset>] [<file> [<format>]] load program file to target memory", |

|

| ||

"VERIFY [<offset>] [<file> [<format>]] verify a program file to target memory", |

| ||||

"PROG | [<offset>] [<file> [<format>]] program flash memory", |

|

| ||

" |

| <format> : SREC, BIN, AOUT, ELF or COFF", |

|

| |

"ERASE | [<address> [<mode>]] | erase a flash memory sector, chip or block", |

|

| |

" |

| <mode> : | CHIP, BLOCK or SECTOR (default is sector)", |

|

|

"ERASE | <addr> <step> <count> | erase multiple flash sectors", |

|

| |

"UNLOCK [<addr> [<delay>]] | unlock a flash sector", |

|

| ||

"UNLOCK <addr> <step> <count> | unlock multiple flash sectors", |

|

| ||

"FLASH | <type> <size> <bus> | change flash configuration", |

|

| |

"FENA | <addr> <size> | enable autoamtic programming to flash memory", |

|

| |

"FDIS |

| disable autoamtic programming to flash memory", |

|

| |

"DELAY | <ms> | delay for a number of milliseconds", |

|

| |

"MEMACC {CORE AHB [<hprot>]} |

|

| |||

"SELECT <core> | change the current core", |

|

| ||

"HOST | <ip> | change IP address of program file host", |

|

| |

"PROMPT <string> | defines a new prompt string", |

|

| ||

"CONFIG | display or update BDI configuration", |

|

| ||

"CONFIG <file> [<hostIP> [<bdiIP> [<gateway> [<mask>]]]]", |

|

| |||

"HELP |

| display command list", |

|

| |

"QUIT |

| terminate the Telnet session" |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

© Copyright | V 1.04 |