System Architecture

System Architecture

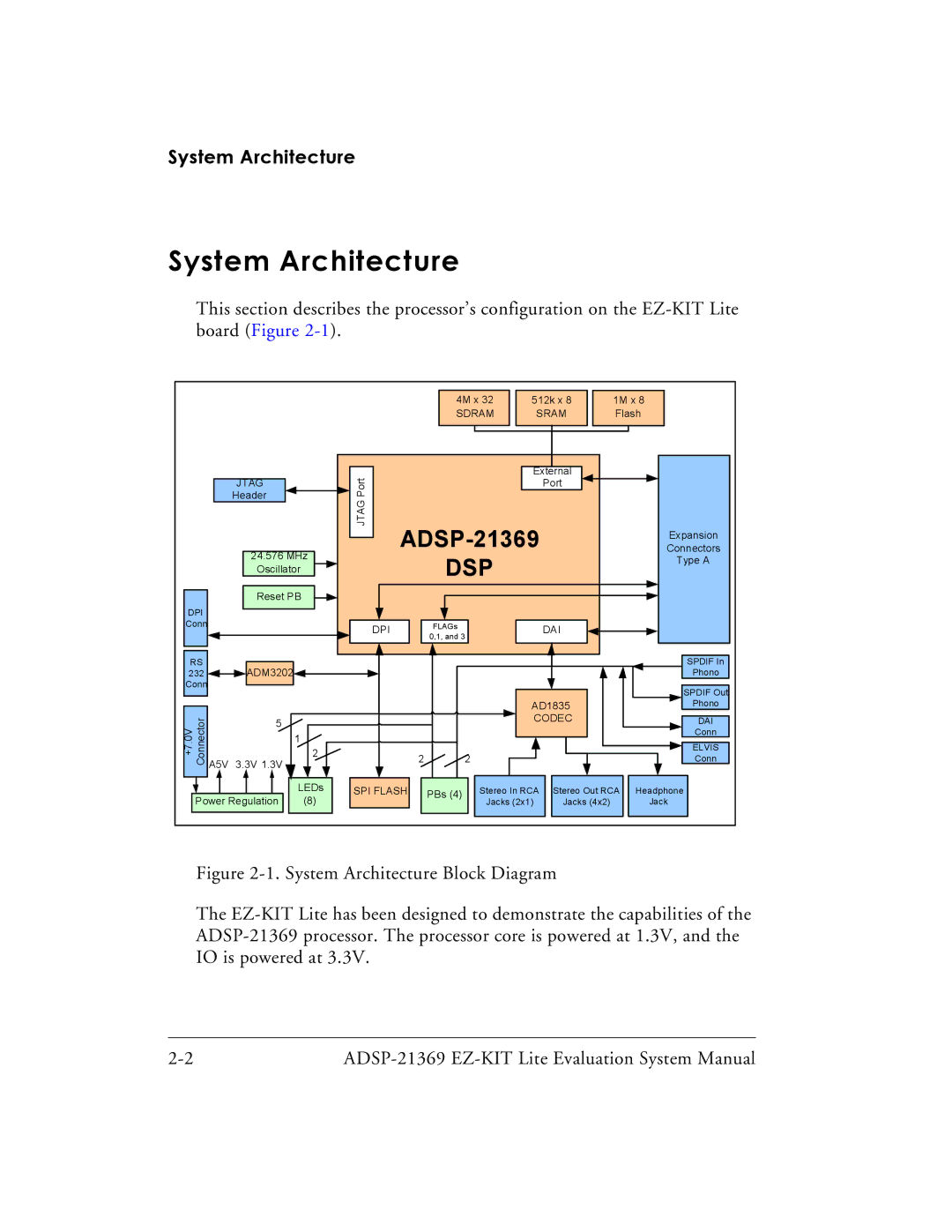

This section describes the processor’s configuration on the

|

|

|

|

| 4M x 32 | 512k x 8 | 1M x 8 | |||

|

|

|

|

| SDRAM | SRAM | Flash | |||

|

|

|

| Port |

|

| External |

|

| |

|

| JTAG |

|

|

|

| Port |

|

| |

|

| Header |

|

|

|

|

|

|

| |

|

|

| JTAG |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| Expansion | ||||

|

| 24.576 MHz |

|

| Connectors | |||||

|

|

| DSP |

|

|

| Type A | |||

|

| Oscillator |

|

|

|

|

| |||

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| ||

|

| Reset PB |

|

|

|

|

|

|

|

|

DPI |

|

|

|

|

|

|

|

|

|

|

Conn |

|

|

| DPI | FLAGs |

|

| DAI |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

| 0,1, and 3 |

|

|

|

|

|

RS |

| ADM3202 |

|

|

|

|

|

|

| SPDIF In |

232 |

|

|

|

|

|

|

|

| Phono | |

Conn |

|

|

|

|

|

|

|

|

| SPDIF Out |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| AD1835 |

| Phono | |

+7.0V Connector |

| 5 |

|

|

|

| CODEC |

| DAI | |

| 1 |

|

|

|

|

|

|

| Conn | |

|

|

|

|

|

|

|

| ELVIS | ||

|

| 2 |

| 2 | 2 |

|

|

| ||

A5V | 3.3V 1.3V |

|

|

|

| Conn | ||||

|

|

|

|

|

|

|

|

| ||

|

| LEDs | SPI FLASH | PBs (4) | Stereo In RCA | Stereo Out RCA | Headphone | |||

Power Regulation | (8) |

|

| Jacks (2x1) | Jacks (4x2) |

| Jack | |||

Figure 2-1. System Architecture Block Diagram

The EZ-KIT Lite has been designed to demonstrate the capabilities of the ADSP-21369 processor. The processor core is powered at 1.3V, and the IO is powered at 3.3V.

|