PRELIMINARYCY14B101P

Status Register

The status register bits are listed in Table 3. The status register consists of Ready bit (RDY) and data protection bits BP1, BP0, WEN and WPEN. The RDY bit can be polled to check the Ready/Busy status while a nvSRAM STORE cycle is in progress. The status register can be modified by WRSR instruc-

Table 3. Status Register Format

tion and read by RDSR instruction. However, only WPEN, BP1 and BP0 bits of the Status Register can be modified by using WRSR instruction. WRSR instruction has no effect on WEN and RDY bits. The default value shipped from the factory for BP1, BP2 and WPEN bits is ‘0’.

Bit 7 | Bit 6 |

| Bit 5 |

| Bit 4 | Bit 3 | Bit 2 |

| Bit 1 | Bit 0 | |||||

WPEN (0) | X |

| X |

| X | BP1 (0) | BP0 (0) |

| WEN |

|

|

| |||

| RDY | ||||||||||||||

Table 4. Status Register Bit Definition |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit |

| Definition |

|

|

|

| Description |

|

|

|

|

| |||

Bit 0 | (RDY) |

|

| Ready |

| Read Only bit indicates the ready status of device to perform a memory access. This | |||||||||

|

|

|

|

|

|

| bit is set to “1” by the device while a STORE or Software Recall cycle is in progress. | ||||||||

Bit 1 (WEN) |

| Write Enable |

| WEN indicates if the device is | |||||||||||

|

|

|

|

|

|

| setting WEN = '0' disables all write operations |

|

|

|

|

| |||

Bit 2 (BP0) |

| Block Protect bit ‘0’ | Used for block protection. For details see Table 5 on page 9. |

|

|

| |||||||||

|

|

|

|

|

|

| |||||||||

Bit 3 (BP1) |

| Block Protect bit ‘1’ | Used for block protection. For details see Table 5 on page 9. |

|

|

| |||||||||

Bit 7(WPEN) |

| Write Protect Enable bit | Used for enabling the function of Write Protect Pin | (WP) | . For details see Table 6 on | ||||||||||

|

|

|

|

|

|

| page 10. |

|

|

|

|

|

|

| |

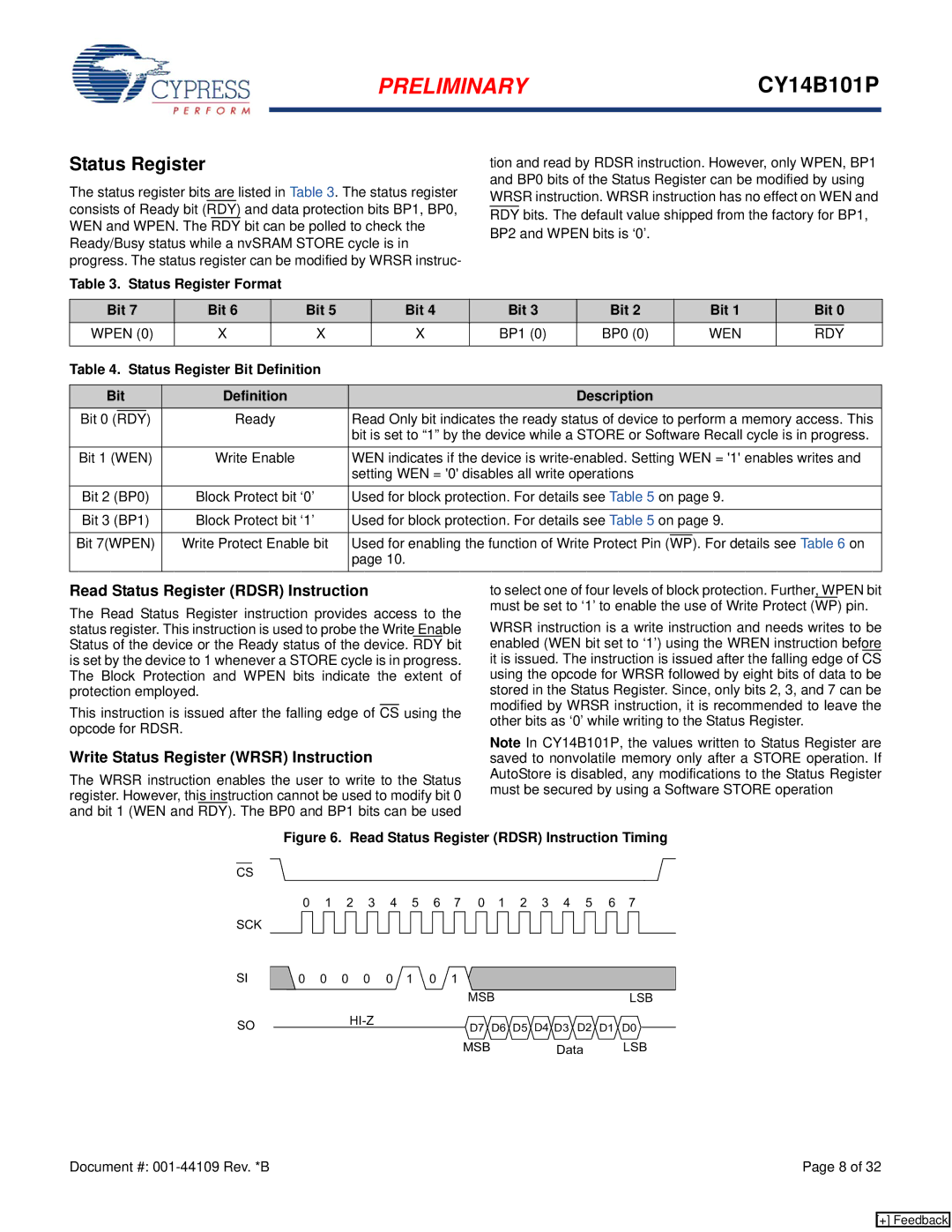

Read Status Register (RDSR) Instruction

The Read Status Register instruction provides access to the status register. This instruction is used to probe the Write Enable Status of the device or the Ready status of the device. RDY bit is set by the device to 1 whenever a STORE cycle is in progress. The Block Protection and WPEN bits indicate the extent of protection employed.

This instruction is issued after the falling edge of CS using the opcode for RDSR.

Write Status Register (WRSR) Instruction

The WRSR instruction enables the user to write to the Status register. However, this instruction cannot be used to modify bit 0 and bit 1 (WEN and RDY). The BP0 and BP1 bits can be used

to select one of four levels of block protection. Further, WPEN bit must be set to ‘1’ to enable the use of Write Protect (WP) pin.

WRSR instruction is a write instruction and needs writes to be enabled (WEN bit set to ‘1’) using the WREN instruction before it is issued. The instruction is issued after the falling edge of CS using the opcode for WRSR followed by eight bits of data to be stored in the Status Register. Since, only bits 2, 3, and 7 can be modified by WRSR instruction, it is recommended to leave the other bits as ‘0’ while writing to the Status Register.

Note In CY14B101P, the values written to Status Register are saved to nonvolatile memory only after a STORE operation. If AutoStore is disabled, any modifications to the Status Register must be secured by using a Software STORE operation

Figure 6. Read Status Register (RDSR) Instruction Timing

CS

SCK

SI

SO

0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7

0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

|

|

|

|

|

|

|

|

|

|

| MSB |

|

|

| LSB |

|

|

|

|

|

| D7 D6 D5 | D4 D3 | D2 | D1 | D0 | |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| MSB | Data |

| LSB | |

Document #: | Page 8 of 32 |

[+] Feedback