|

|

|

|

| PRELIMINARY | CY14B101P | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

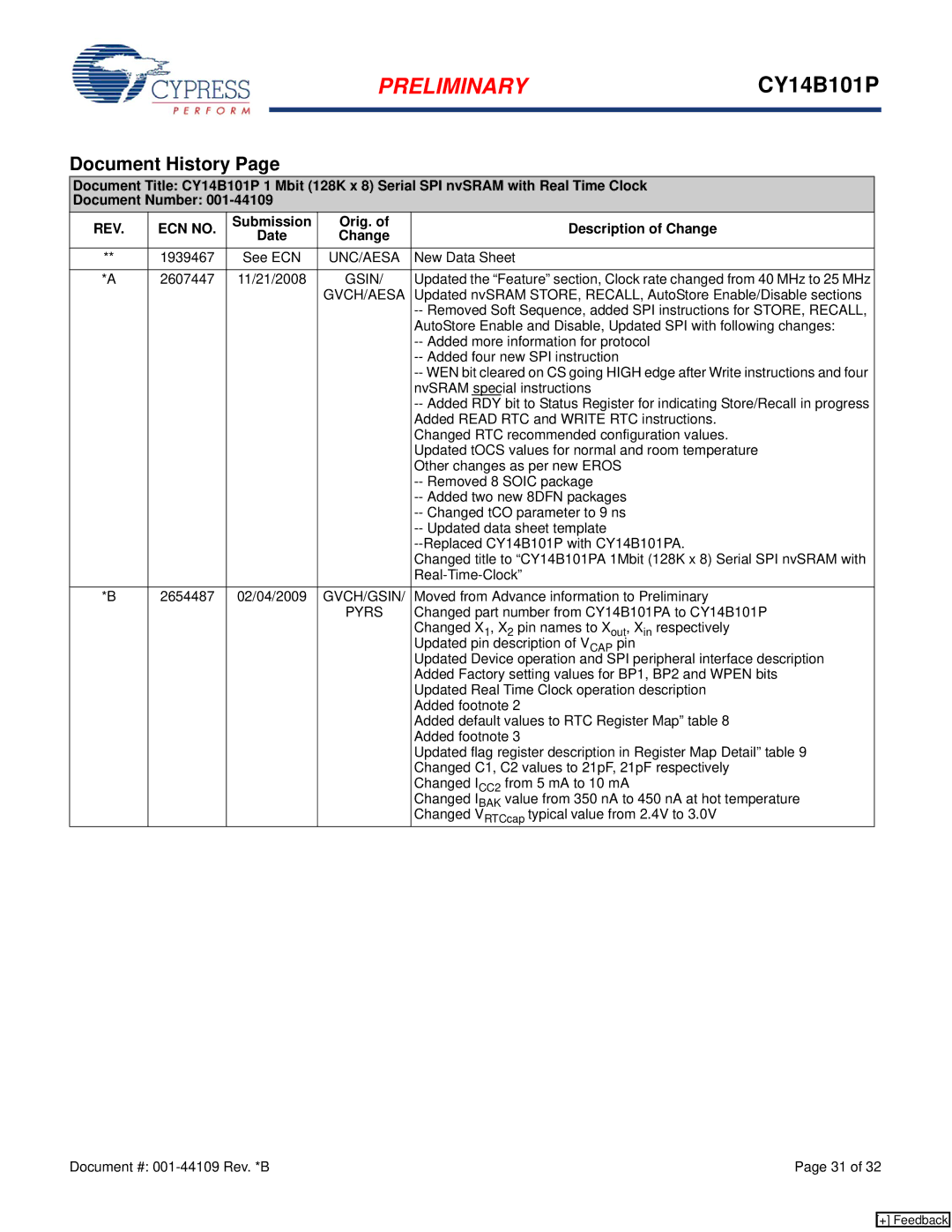

Document History Page |

|

|

|

|

| ||||

Document Title: CY14B101P 1 Mbit (128K x 8) Serial SPI nvSRAM with Real Time Clock |

|

|

| ||||||

Document Number: |

|

|

|

|

| ||||

REV. | ECN NO. | Submission | Orig. of | Description of Change |

|

|

| ||

Date | Change |

|

|

| |||||

|

|

|

|

|

| ||||

** | 1939467 | See ECN | UNC/AESA | New Data Sheet |

|

|

| ||

|

|

|

|

|

| ||||

*A | 2607447 | 11/21/2008 | GSIN/ | Updated the “Feature” section, Clock rate changed from 40 MHz to 25 MHz |

|

| |||

|

|

|

|

| GVCH/AESA | Updated nvSRAM STORE, RECALL, AutoStore Enable/Disable sections |

| ||

|

|

|

|

|

|

| |||

|

|

|

|

|

| AutoStore Enable and Disable, Updated SPI with following changes: |

| ||

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| |||

|

|

|

|

|

| nvSRAM special instructions |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Added READ RTC and WRITE RTC instructions. |

|

|

|

|

|

|

|

|

| Changed RTC recommended configuration values. |

|

|

|

|

|

|

|

|

| Updated tOCS values for normal and room temperature |

|

|

|

|

|

|

|

|

| Other changes as per new EROS |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| Changed title to “CY14B101PA 1Mbit (128K x 8) Serial SPI nvSRAM with |

| ||

|

|

|

|

|

|

|

|

| |

*B | 2654487 | 02/04/2009 | GVCH/GSIN/ | Moved from Advance information to Preliminary |

|

|

| ||

|

|

|

|

| PYRS | Changed part number from CY14B101PA to CY14B101P |

| ||

|

|

|

|

|

| Changed X1, X2 pin names to Xout, Xin respectively |

|

|

|

|

|

|

|

|

| Updated pin description of VCAP pin |

|

|

|

|

|

|

|

|

| Updated Device operation and SPI peripheral interface description |

| ||

|

|

|

|

|

| Added Factory setting values for BP1, BP2 and WPEN bits |

| ||

|

|

|

|

|

| Updated Real Time Clock operation description |

|

|

|

|

|

|

|

|

| Added footnote 2 |

|

|

|

|

|

|

|

|

| Added default values to RTC Register Map” table 8 |

|

|

|

|

|

|

|

|

| Added footnote 3 |

|

|

|

|

|

|

|

|

| Updated flag register description in Register Map Detail” table 9 |

| ||

|

|

|

|

|

| Changed C1, C2 values to 21pF, 21pF respectively |

|

|

|

|

|

|

|

|

| Changed ICC2 from 5 mA to 10 mA |

|

|

|

|

|

|

|

|

| Changed IBAK value from 350 nA to 450 nA at hot temperature |

| ||

|

|

|

|

|

| Changed VRTCcap typical value from 2.4V to 3.0V |

|

|

|

Document #: | Page 31 of 32 |

[+] Feedback