PRELIMINARYCY14B101P

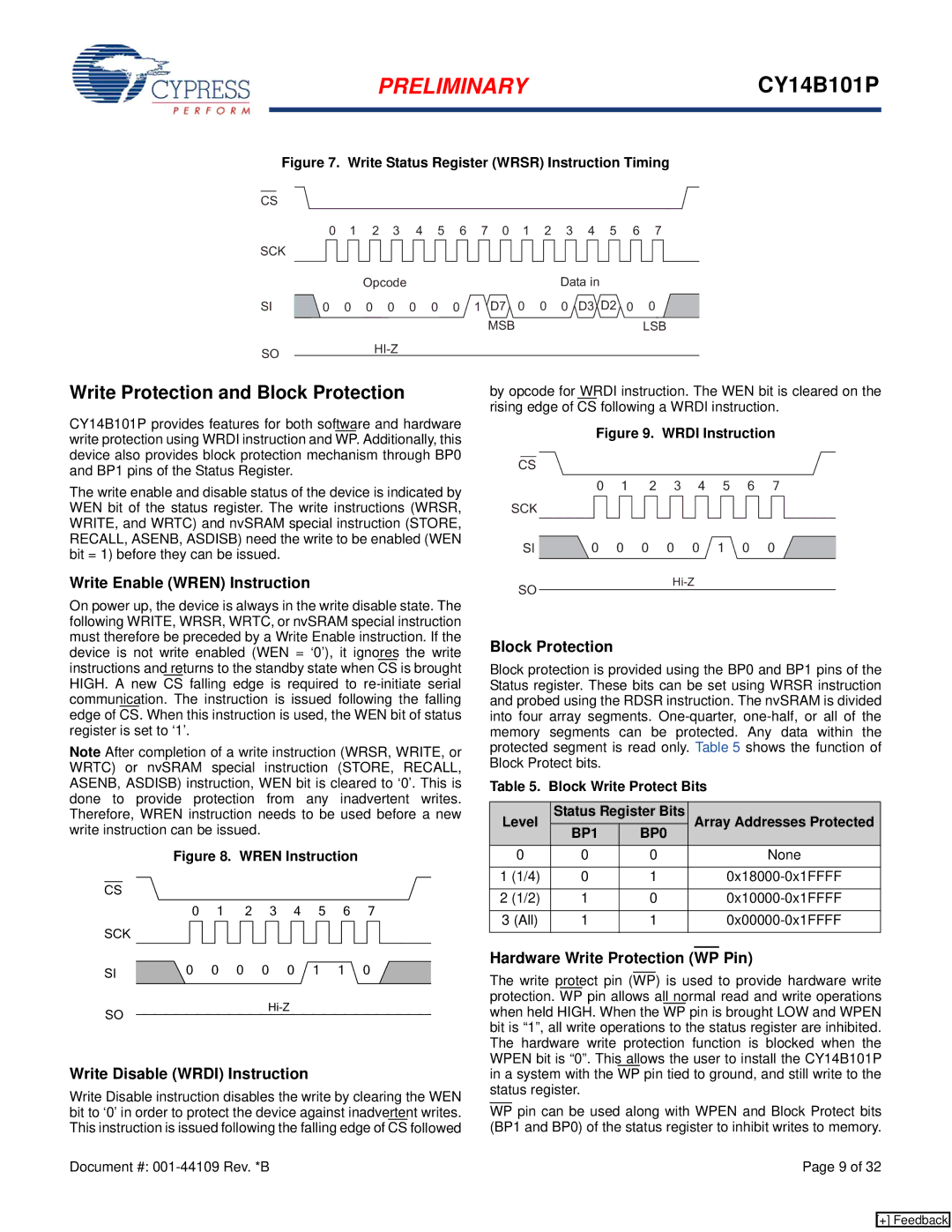

Figure 7. Write Status Register (WRSR) Instruction Timing

CS

0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7

SCK

|

|

| Opcode |

|

|

|

|

|

|

| Data in |

|

| ||

SI | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | D7 | 0 | 0 | 0 | D3 D2 | 0 | 0 |

|

|

|

|

|

|

|

|

| MSB |

|

|

|

|

| LSB |

SOHI-Z

Write Protection and Block Protection

CY14B101P provides features for both software and hardware write protection using WRDI instruction and WP. Additionally, this device also provides block protection mechanism through BP0 and BP1 pins of the Status Register.

The write enable and disable status of the device is indicated by WEN bit of the status register. The write instructions (WRSR, WRITE, and WRTC) and nvSRAM special instruction (STORE, RECALL, ASENB, ASDISB) need the write to be enabled (WEN bit = 1) before they can be issued.

Write Enable (WREN) Instruction

by opcode for WRDI instruction. The WEN bit is cleared on the rising edge of CS following a WRDI instruction.

Figure 9. WRDI Instruction

CS |

|

|

|

|

|

|

|

|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

SCK |

|

|

|

|

|

|

|

|

SI | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

SO |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

On power up, the device is always in the write disable state. The following WRITE, WRSR, WRTC, or nvSRAM special instruction must therefore be preceded by a Write Enable instruction. If the device is not write enabled (WEN = ‘0’), it ignores the write instructions and returns to the standby state when CS is brought HIGH. A new CS falling edge is required to

Note After completion of a write instruction (WRSR, WRITE, or WRTC) or nvSRAM special instruction (STORE, RECALL, ASENB, ASDISB) instruction, WEN bit is cleared to ‘0’. This is done to provide protection from any inadvertent writes. Therefore, WREN instruction needs to be used before a new write instruction can be issued.

Figure 8. WREN Instruction

CS |

|

|

|

|

|

|

|

|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

SCK |

|

|

|

|

|

|

|

|

SI | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

SO |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

Write Disable (WRDI) Instruction

Write Disable instruction disables the write by clearing the WEN bit to ‘0’ in order to protect the device against inadvertent writes. This instruction is issued following the falling edge of CS followed

Block Protection

Block protection is provided using the BP0 and BP1 pins of the Status register. These bits can be set using WRSR instruction and probed using the RDSR instruction. The nvSRAM is divided into four array segments.

Table 5. Block Write Protect Bits

Level | Status Register Bits | Array Addresses Protected | ||

BP1 | BP0 | |||

|

| |||

0 | 0 | 0 | None | |

|

|

|

| |

1 (1/4) | 0 | 1 | ||

|

|

|

| |

2 (1/2) | 1 | 0 | ||

|

|

|

| |

3 (All) | 1 | 1 | ||

|

|

|

| |

Hardware Write Protection (WP Pin)

The write protect pin (WP) is used to provide hardware write protection. WP pin allows all normal read and write operations when held HIGH. When the WP pin is brought LOW and WPEN bit is “1”, all write operations to the status register are inhibited. The hardware write protection function is blocked when the WPEN bit is “0”. This allows the user to install the CY14B101P in a system with the WP pin tied to ground, and still write to the status register.

WP pin can be used along with WPEN and Block Protect bits (BP1 and BP0) of the status register to inhibit writes to memory.

Document #: | Page 9 of 32 |

[+] Feedback