PRELIMINARYCY14B101P

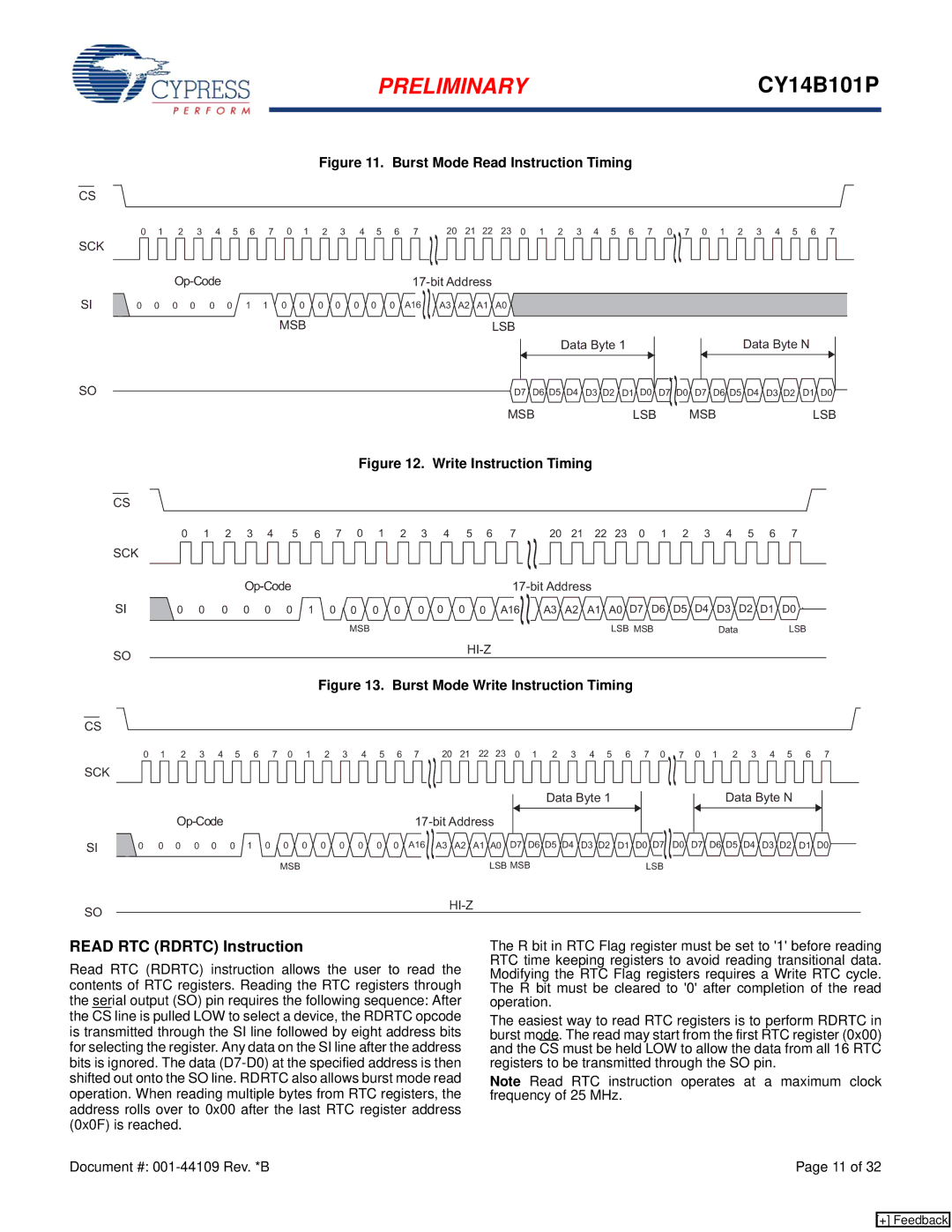

Figure 11. Burst Mode Read Instruction Timing

CS

SCK

SI

SO

0 | 1 |

| 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 20 | 21 | 22 | 23 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 |

| 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ~~ |

|

|

|

|

|

|

|

|

|

|

|

| ~ |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ~ |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | A16 |

| A3 | A2 | A1 | A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MSB |

|

|

|

|

| ~~ |

|

| LSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Data Byte 1 |

|

|

|

|

|

|

| Data Byte N |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D7 | D6 D5 D4 | D3 D2 | D1 D0 | D7 D0 | D7 | D6 | D5 D4 | D3 D2 | D1 D0 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MSB |

|

|

|

| LSB | ~~ | MSB |

|

|

|

| LSB | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

CS

SCK

SI

SO

Figure 12. Write Instruction Timing

0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 20 | 21 | 22 | 23 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ~~ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | A16 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

| MSB |

|

|

|

|

|

| ~ ~ |

|

|

| LSB MSB |

|

| Data |

|

| LSB | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Figure 13. Burst Mode Write Instruction Timing

CS

SCK

SI

SO

0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 20 | 21 | 22 | 23 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 |

| 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ~~ |

|

|

|

|

|

|

|

|

|

|

| ~ |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Data Byte 1 |

|

|

| ~ |

|

| Data Byte N |

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ~~ |

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ~ ~ |

|

|

|

| D6 D5 D4 |

|

|

|

|

|

| D6 D5 | D4 |

|

|

|

| ||||||

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | A16 | A3 | A2 | A1 A0 | D7 | D3 D2 | D1 | D0 D7 | D0 | D7 | D3 D2 | D1 | D0 | |||||||||||

|

|

|

|

|

|

|

| MSB |

|

|

|

|

|

|

|

|

|

| LSB MSB |

|

|

|

|

| LSB |

|

|

|

|

|

|

|

|

|

| |||

READ RTC (RDRTC) Instruction

Read RTC (RDRTC) instruction allows the user to read the contents of RTC registers. Reading the RTC registers through the serial output (SO) pin requires the following sequence: After the CS line is pulled LOW to select a device, the RDRTC opcode is transmitted through the SI line followed by eight address bits for selecting the register. Any data on the SI line after the address bits is ignored. The data

The R bit in RTC Flag register must be set to '1' before reading RTC time keeping registers to avoid reading transitional data. Modifying the RTC Flag registers requires a Write RTC cycle. The R bit must be cleared to '0' after completion of the read operation.

The easiest way to read RTC registers is to perform RDRTC in burst mode. The read may start from the first RTC register (0x00) and the CS must be held LOW to allow the data from all 16 RTC registers to be transmitted through the SO pin.

Note Read RTC instruction operates at a maximum clock frequency of 25 MHz.

Document #: | Page 11 of 32 |

[+] Feedback