|

|

|

|

|

|

|

|

| CY7C1360C |

|

|

|

|

|

|

|

|

| CY7C1362C |

. |

|

|

|

|

|

|

|

|

|

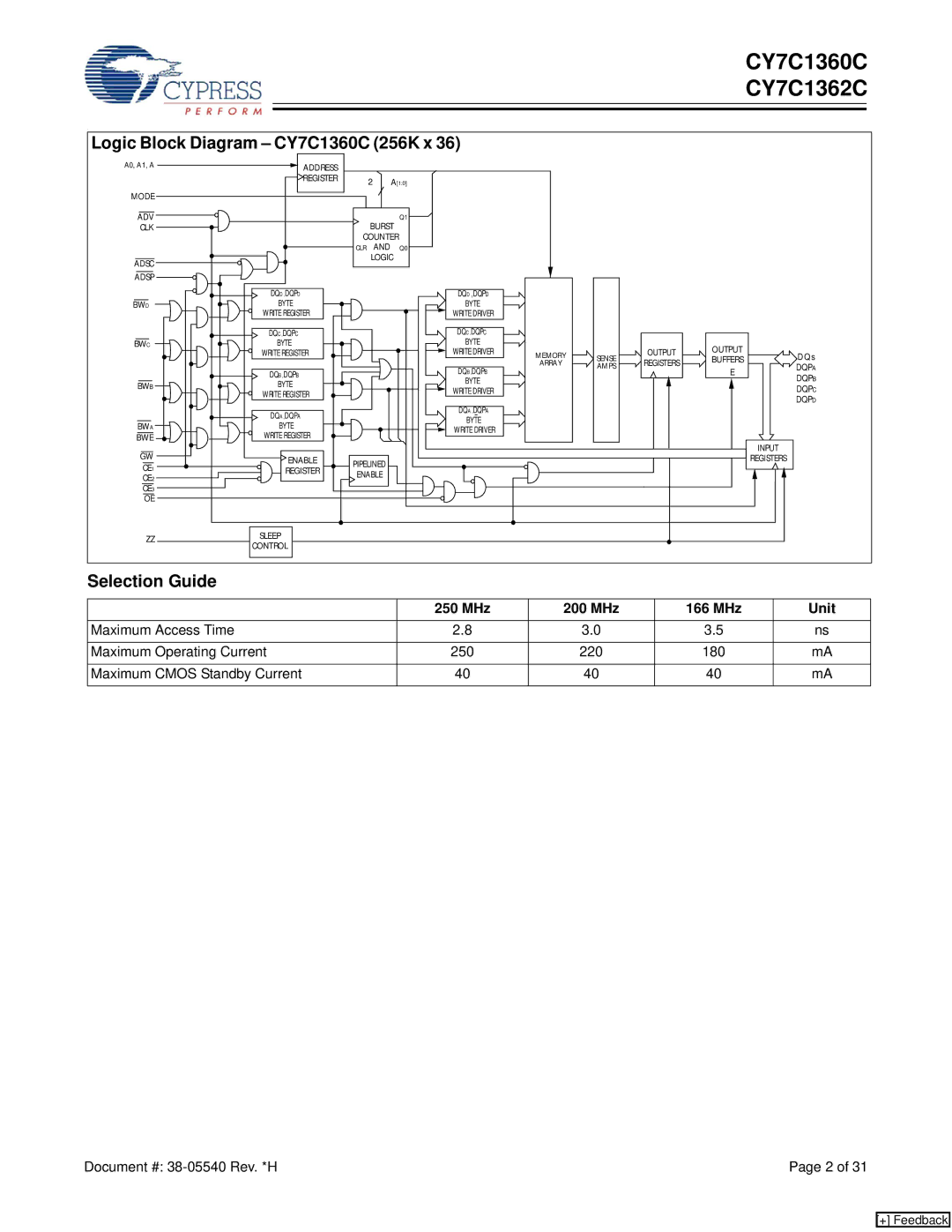

Logic Block Diagram – CY7C1360C (256K x 36) |

|

|

|

|

| ||||

A0, A1, A | ADDRESS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| REGISTER |

| 2 | A[1:0] |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

MODE |

|

|

|

|

|

|

|

|

|

ADV |

|

|

| Q1 |

|

|

|

|

|

CLK |

|

| BURST |

|

|

|

|

| |

|

| COUNTER |

|

|

|

|

| ||

|

| CLR | AND | Q0 |

|

|

|

|

|

ADSC |

|

| LOGIC |

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

ADSP |

|

|

|

|

|

|

|

|

|

| DQD ,DQPD |

|

| DQD ,DQPD |

|

|

|

|

|

BWD | BYTE |

|

| BYTE |

|

|

|

|

|

| WRITE REGISTER |

|

| WRITE DRIVER |

|

|

|

|

|

| DQC ,DQPC |

|

| DQC ,DQPC |

|

|

|

|

|

BWC | BYTE |

|

| BYTE |

|

|

| OUTPUT |

|

| WRITE REGISTER |

|

| WRITE DRIVER | MEMORY | SENSE | OUTPUT | DQs | |

|

|

| BUFFERS | ||||||

|

|

|

|

| ARRAY | REGISTERS | |||

|

|

|

| DQB ,DQPB | AMPS | E | DQPA | ||

| DQB ,DQPB |

|

|

|

| ||||

|

|

|

|

|

| DQPB | |||

BWB | BYTE |

|

| BYTE |

|

|

|

| |

|

|

|

|

|

| DQPC | |||

|

| WRITE DRIVER |

|

|

|

| |||

| WRITE REGISTER |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| DQPD | |

|

|

|

|

|

|

|

|

| |

| DQA ,DQPA |

|

| DQA ,DQPA |

|

|

|

|

|

|

|

| BYTE |

|

|

|

|

| |

BWA | BYTE |

|

|

|

|

|

|

| |

|

| WRITE DRIVER |

|

|

|

|

| ||

BWE | WRITE REGISTER |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| ||

GW |

|

|

|

|

|

|

|

| INPUT |

ENABLE | PIPELINED |

|

|

|

|

| REGISTERS | ||

CE1 | REGISTER |

|

|

|

|

|

| ||

ENABLE |

|

|

|

|

|

| |||

CE2 |

|

|

|

|

|

| |||

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| |

CE3 |

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

|

|

ZZ | SLEEP |

|

|

|

|

|

|

|

|

CONTROL |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

Selection Guide

| 250 MHz | 200 MHz | 166 MHz | Unit |

Maximum Access Time | 2.8 | 3.0 | 3.5 | ns |

|

|

|

|

|

Maximum Operating Current | 250 | 220 | 180 | mA |

|

|

|

|

|

Maximum CMOS Standby Current | 40 | 40 | 40 | mA |

|

|

|

|

|

Document #: | Page 2 of 31 |

[+] Feedback